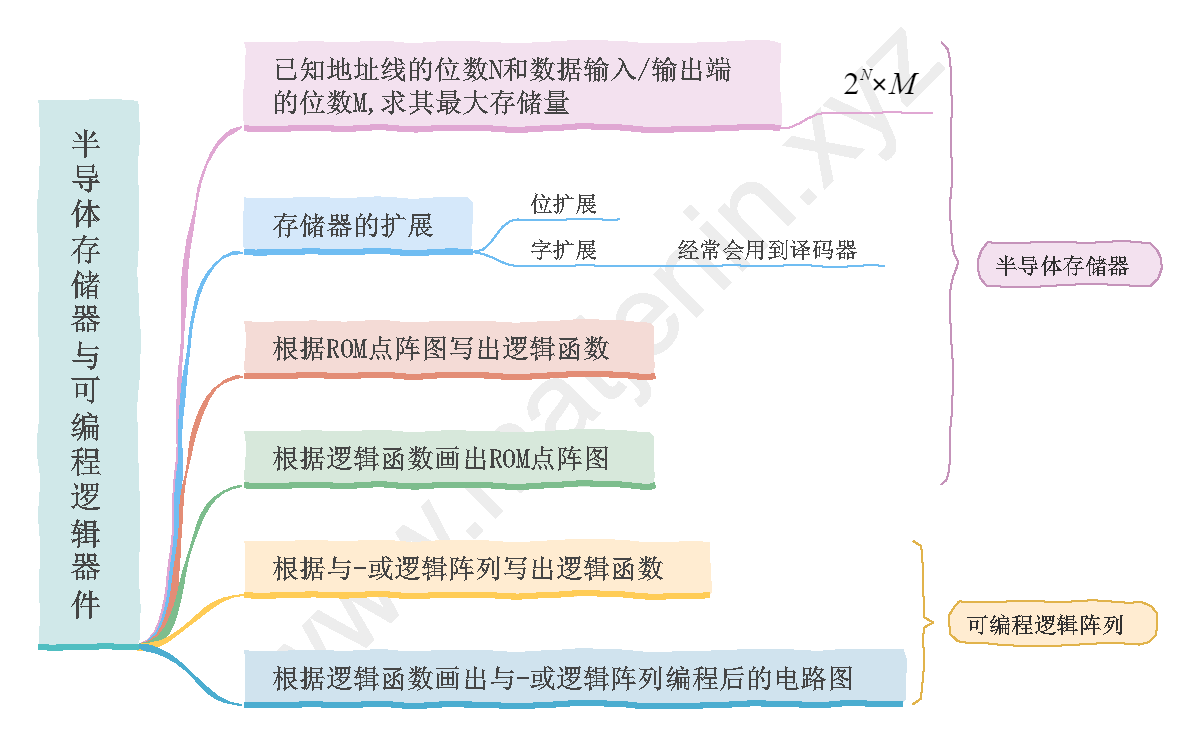

数电 第七章:存储器和可编程逻辑器件

考纲:熟悉可编程逻辑器件组成、原理及应用;掌握存储器容量扩展方法。

7.1 存储器

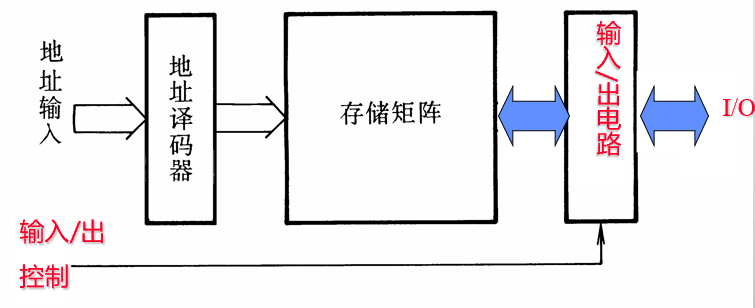

半导体存储器:一种能存储大量二值信息的半导体器件。

分类:

①. 从存/取功能分:

- 只读存储器:掩膜ROM,可编程ROM,可擦除的可编程EPROM

- 随机读/写:静态RAM,动态RAM

②. 从工艺分:

- 双极型

- MOS型

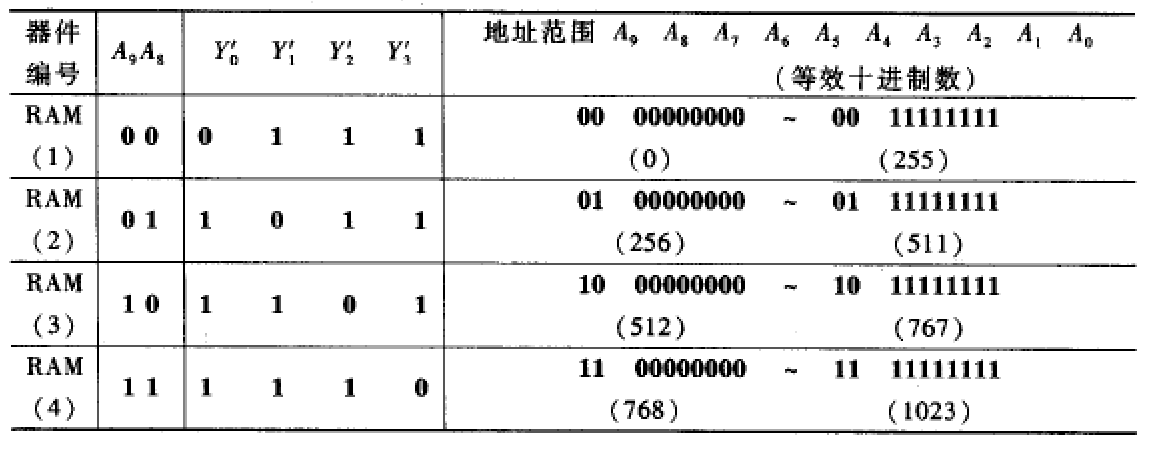

存储器容量的扩展

存储容量:

- 位容量:每个数据位数,以数据线的多少来表示:$D_0D_1…D_n$或$I/O_0I/O_1…I/O_n$

- 字容量:数据字数,以地址线的多少表示:$A_0A_1…A_n$

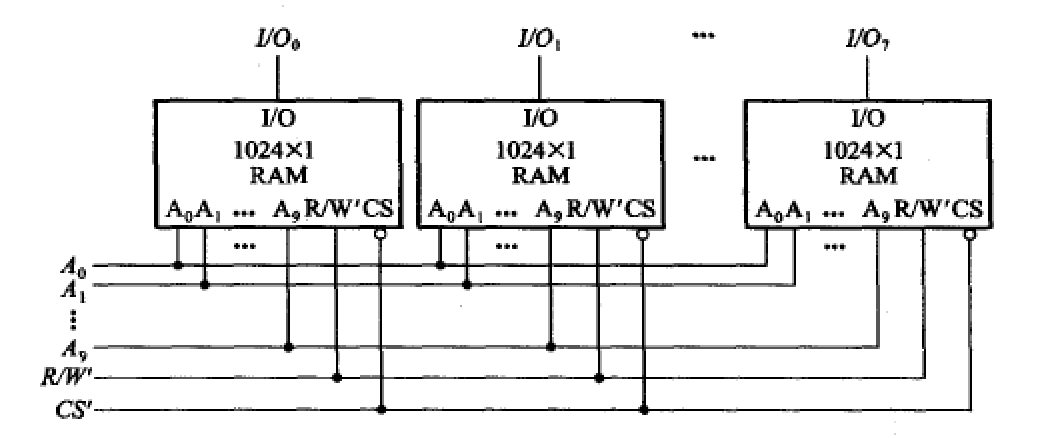

位扩展

如果每片ROM和RAM中的字数已经够用而每个字的位数不够用,则应采用位扩展的连接方式。

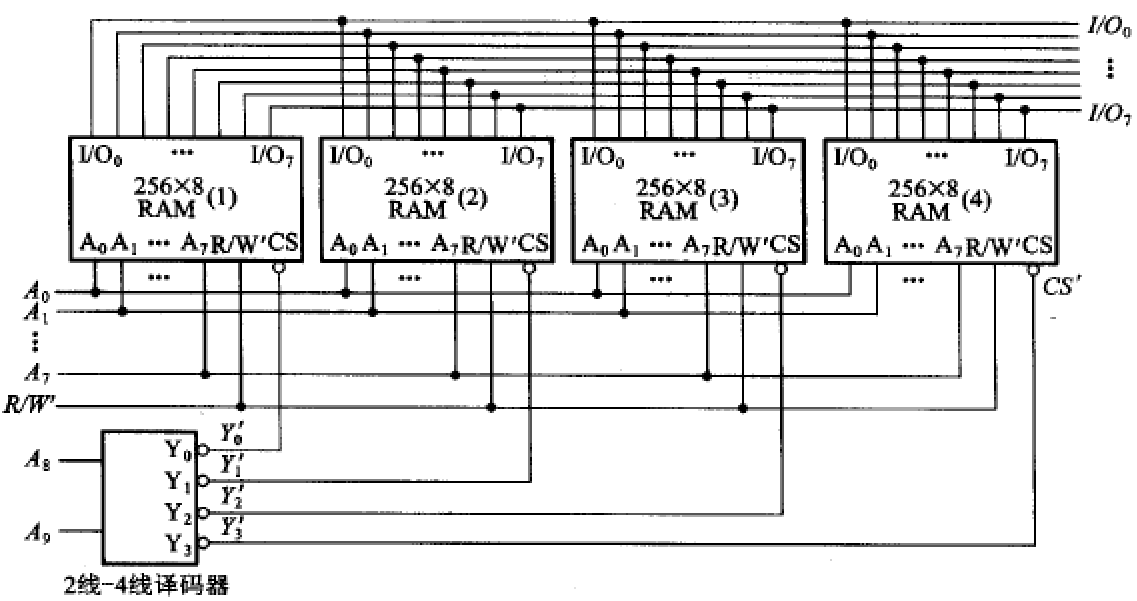

字扩展

如果每片存储器的数据位数够用而字数不够用,则需要采用字扩展方式。

7.2 可编程逻辑器件

可编程逻辑器件:PLD

分类:

- PAL: 可编程阵列逻辑

- FPLA:现场可编程阵列逻辑

- GAL: 通用阵列逻辑

- EPLD: 可擦除的可编程逻辑器件

- CPLD: 复杂的可编程逻辑器件

- FPGA: 现场可编程门阵列

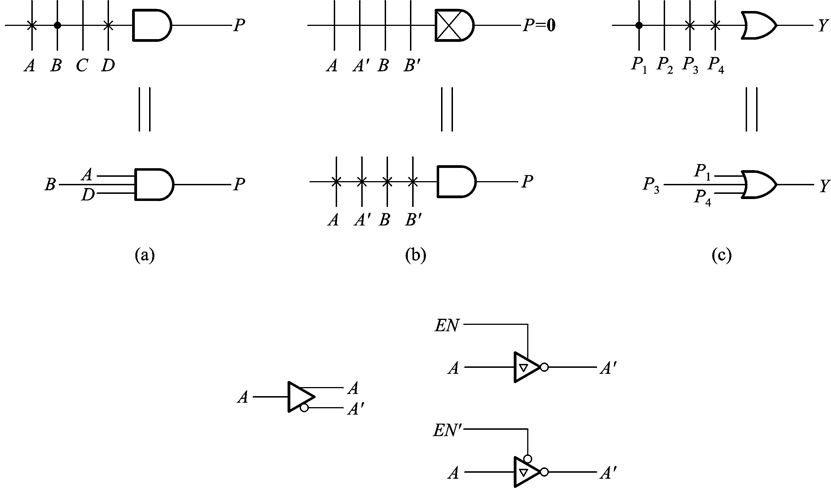

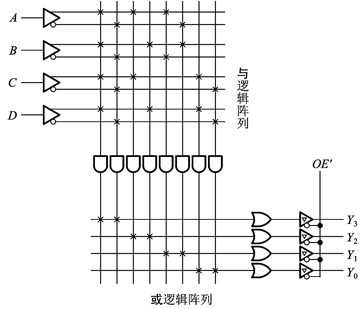

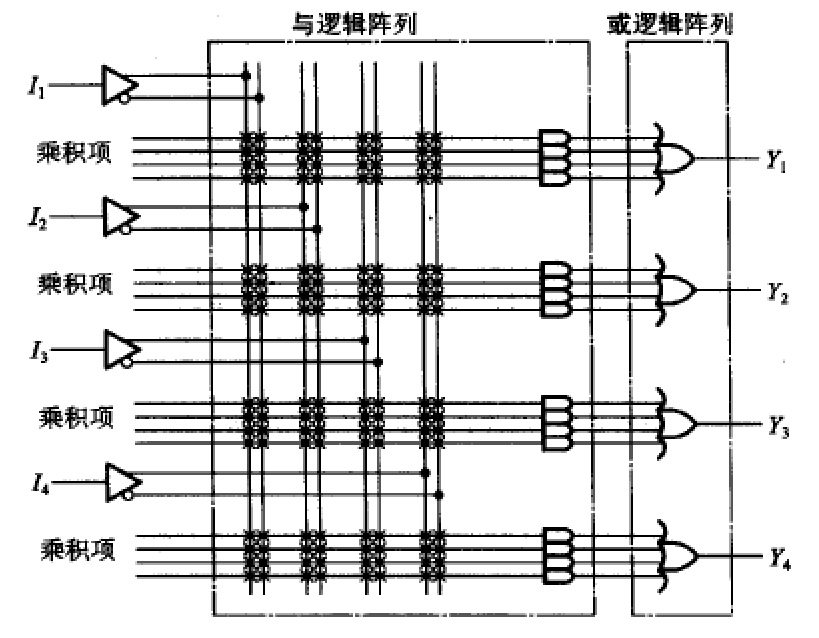

7.2.1 现场编程逻辑阵列FPLA

是最早使用的PLD。

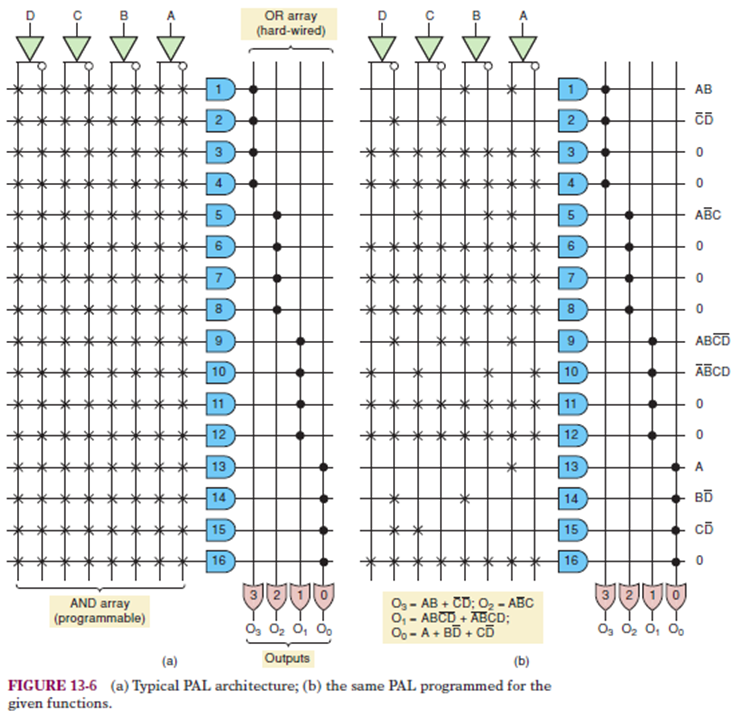

7.2.2 可编程阵列逻辑PAL

采用双极型熔丝工艺,工作速度较高。出厂编程前,所有交叉点均有熔丝。

适用环境:小批量定型产品中的中规模逻辑电路

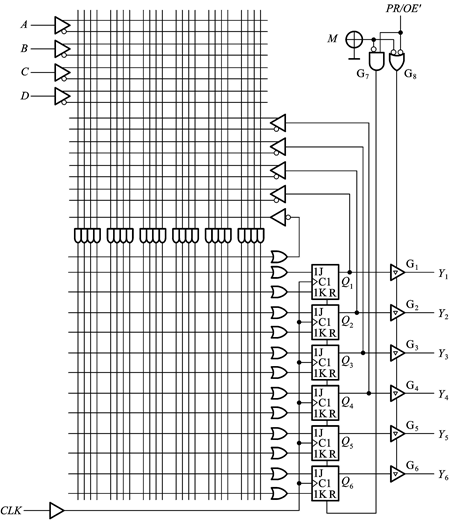

7.2.3 通用阵列逻辑GAL

采用电可擦除的CMOS(E2CMOS)制作,可用电压信号擦除并可重新编程。

结构:可编程“与阵列”(编程单元)+固定“或”阵列+可编程输出电路(OLMC,输出逻辑宏单元)

适用环境:产品研制过程中需要不断修改的中、小规模逻辑电路。

通过编程可将OLMC设置成不同的工作状态,GAL就可在功能上代替前面讨论过的PAL各种输出类型及其派生类型。

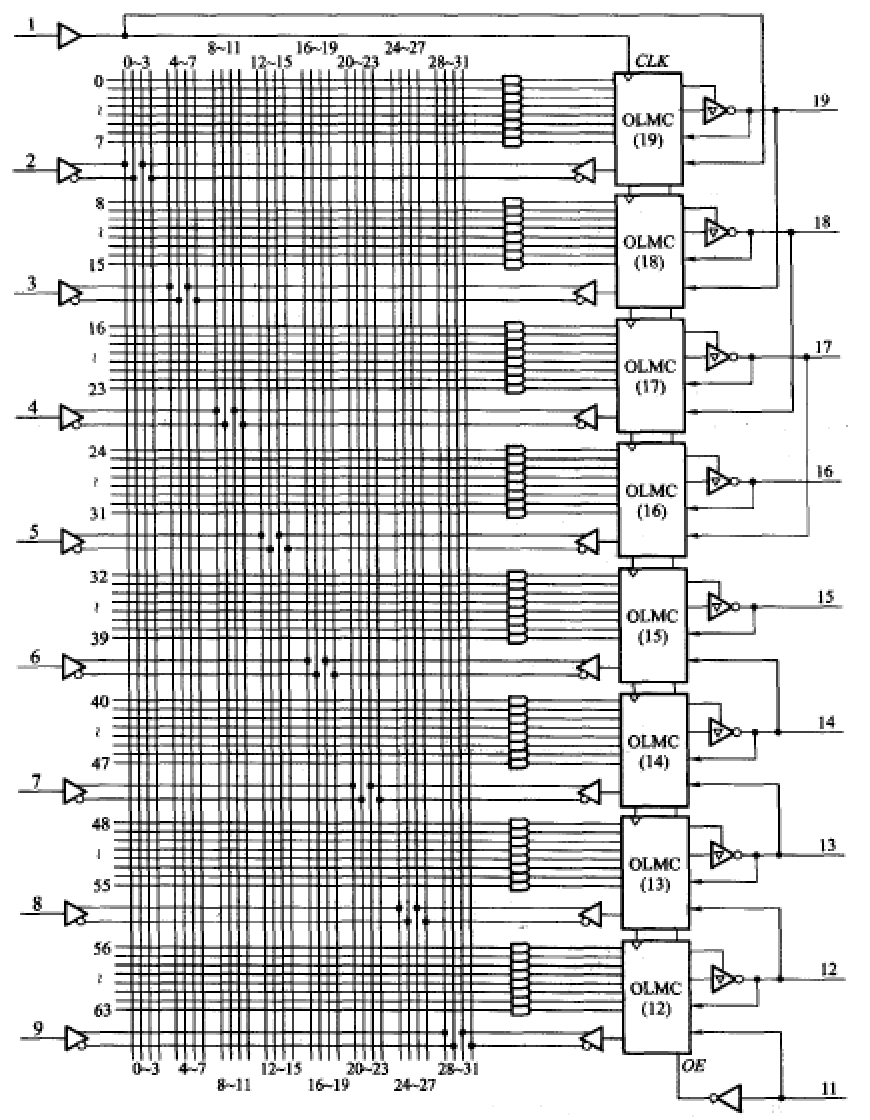

7.2.4 可擦除的可编程逻辑阵列EPLD

基本结构和PAL、GAL类似,由可编程的与逻辑阵列、固定的或逻辑阵列和输出逻辑宏单元(OLMC)组成。

相比PAL、GAL之下的特点:低功耗、高噪声容限,集成度高,灵活性强

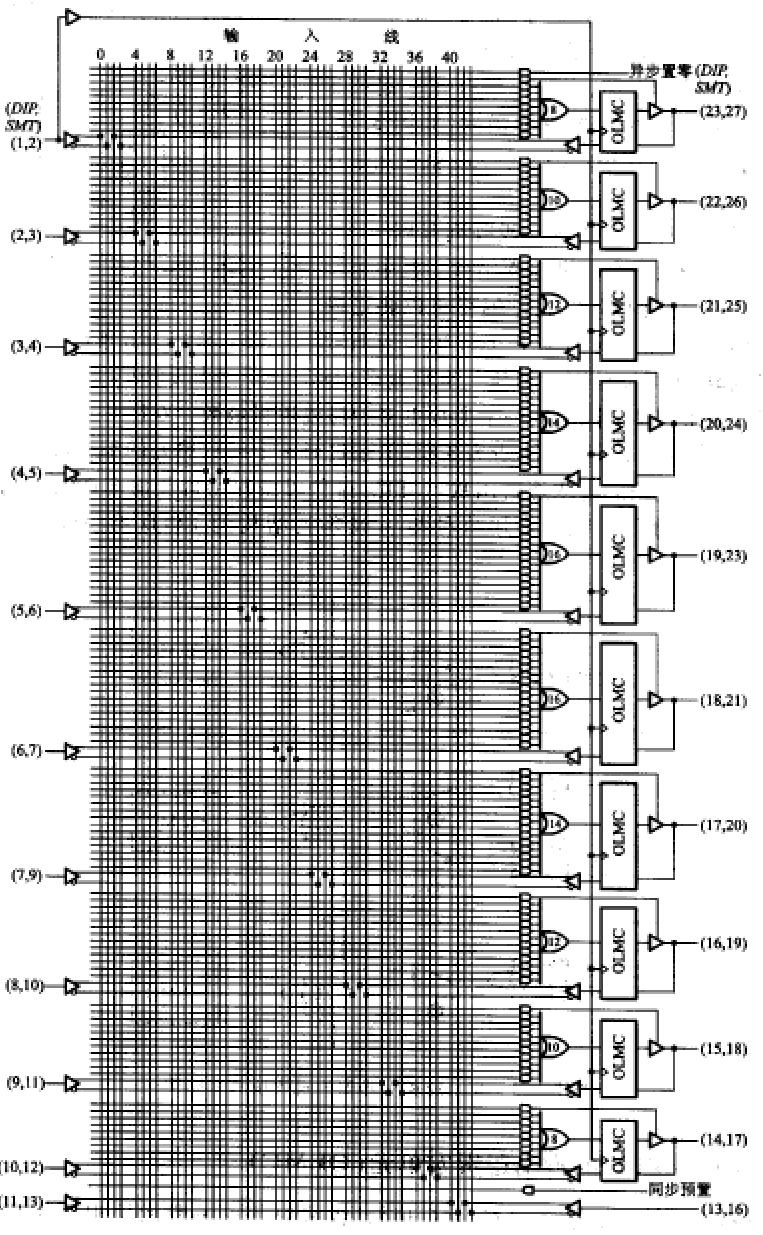

7.2.5 复杂的可编程逻辑器件CPLD

将若干个类似于GAL的功能模块和实现互连的开关矩阵集成于同一芯片上,就形成了所谓的CPLD。CPLD多采用E2CMOS工艺制作。

同时,为了使用方便,越来越多的CPLD都做成了在系统可编程器件isp-PLD

一般结构:若干个可编程的逻辑模块、输入/输出模块和一些可编程的内部连线阵列组成。

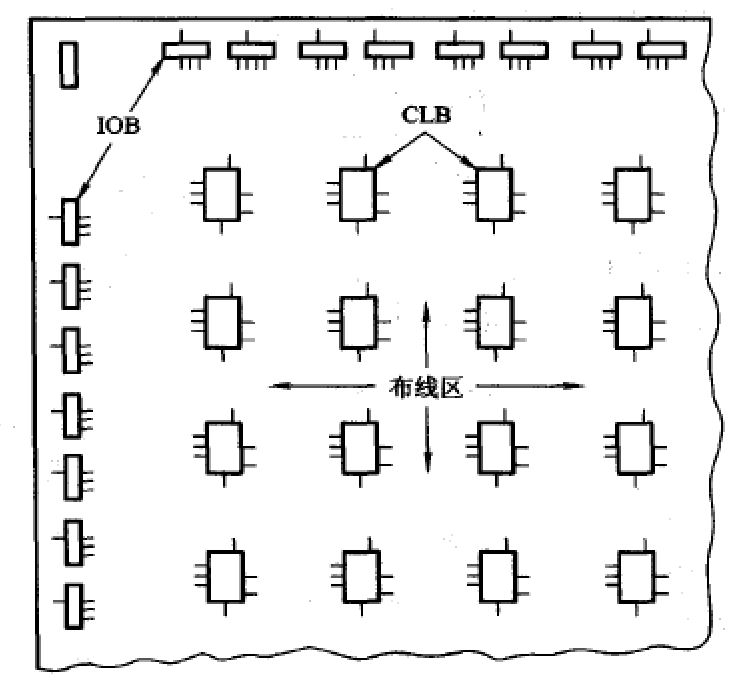

7.2.6 现场可编程门阵列(FPGA)

电路结构形式:由若干独立的可编程逻辑模块组成

上图由三种可编程单元和一个用于存放编程数据的静态存储器组成。三种可编程的单元是输入/输出模块IOB、可编程逻辑模块CLB和互连资源IR.

数据通常都存放在一片EPROM中,掉电丢失,而且要读出并送到FPGA的SRAM中,因而不便于保密。

题型总结