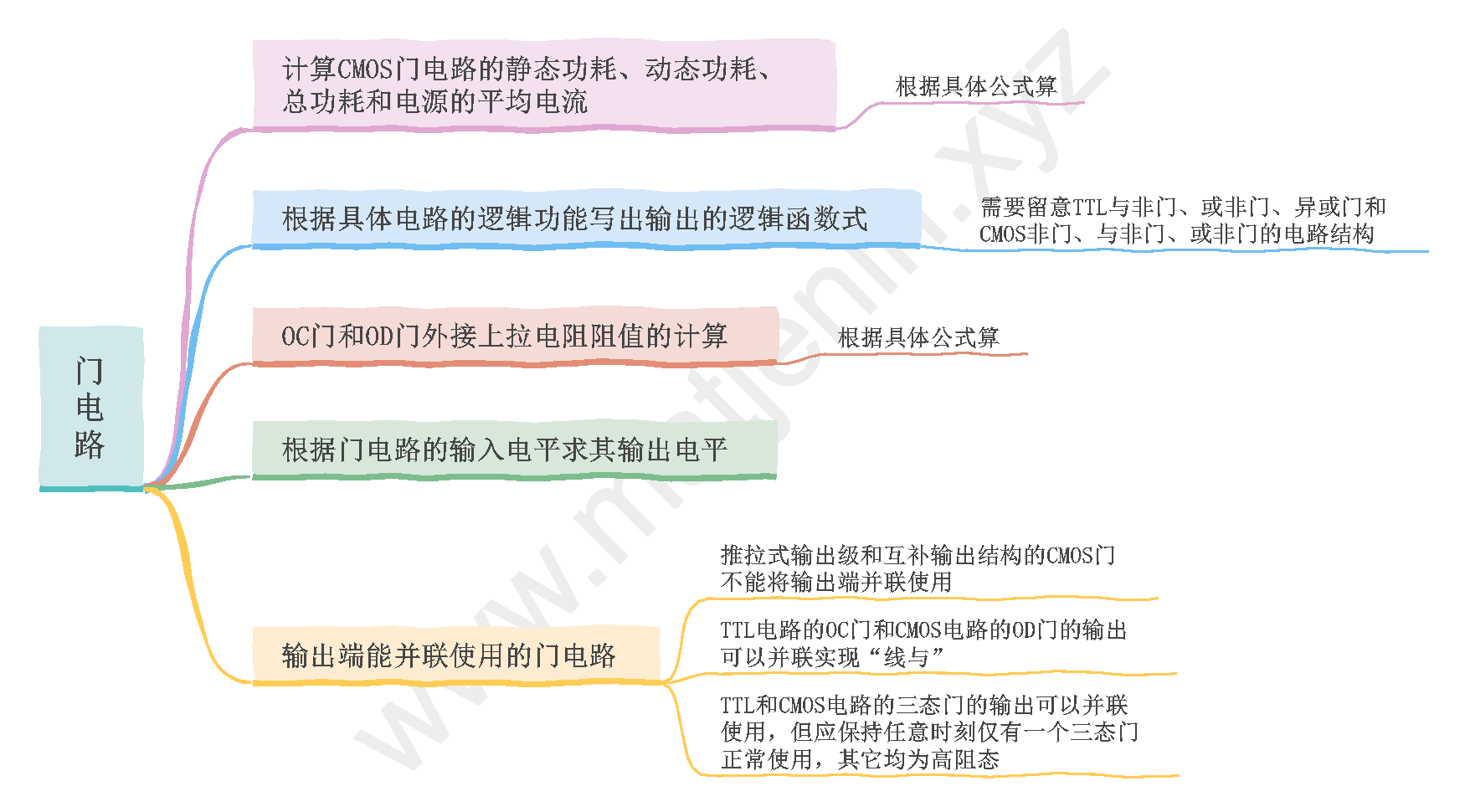

数电 第三章:门电路

考纲:熟悉TTL集成门电路和CMOS集成门电路的电路组成和原理;掌握 TTL电路和 CMOS电路的主要参数的物理意义、输入输出特性和输入输出等效电路;掌握集成电路使用的注意事项。

用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路

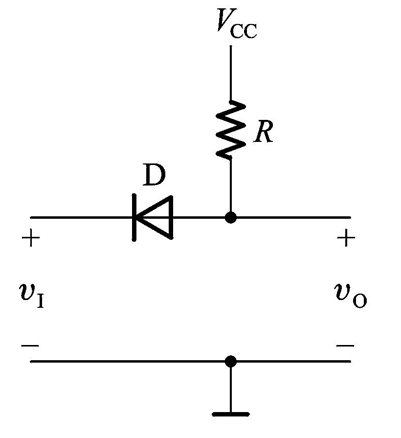

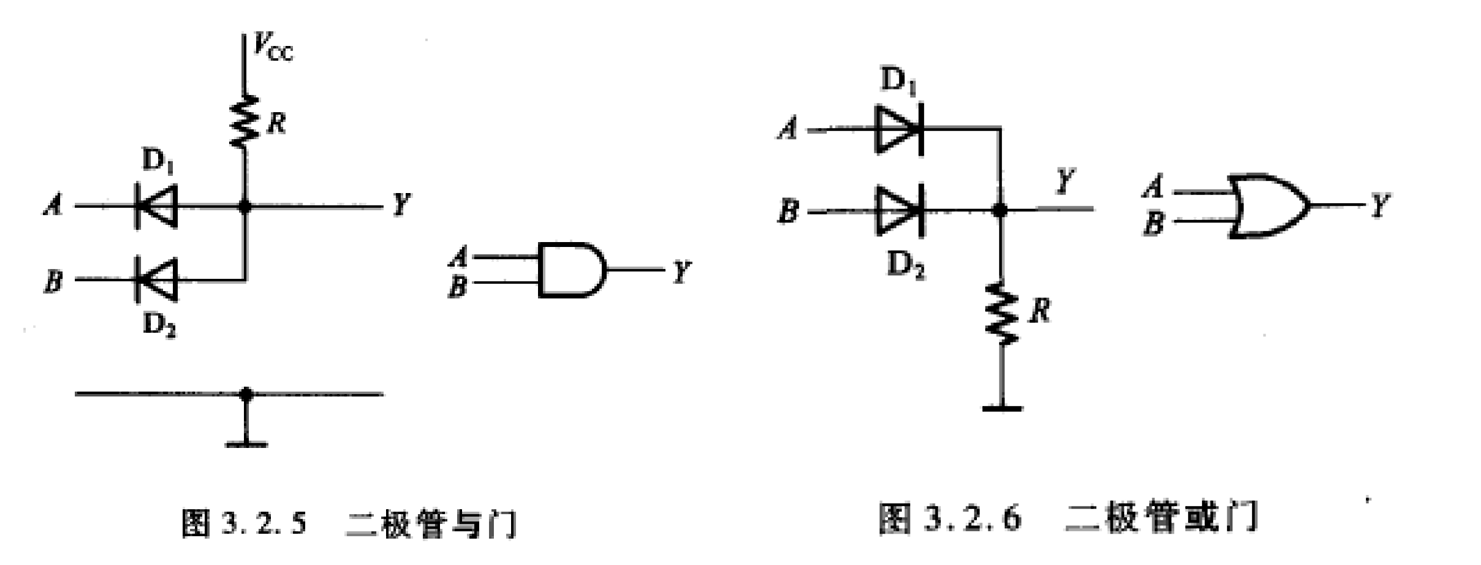

3.1 半导体二极管门电路

这部分考纲里没有,但作为比较基础的知识稍微展开了一下

二极管的开关特性:

$V_I=V_{IH}$:$D$截止,$V_O=V_{OH}=V_{CC}$

$V_I=V_{IL}$:$D$导通,$V_O=V_{OL}=0.7V$

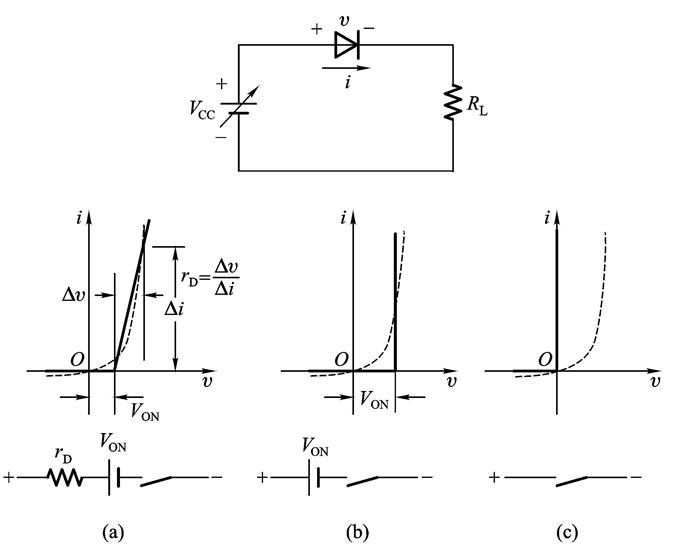

二极管伏安特性的近似方法:

在这里只需要注意上图中的$(b)$,对应当二极管的正向导通压降和外加电源电压相比不能忽略, 且与外接电阻相比二极管的正向电阻可以忽略的情况。

当加到二极管两端的电压小于$V_{ON}$时,流过二极管的电流近似地看作为$0$;

当外加电压大于$V_{ON}$时,二极管导通,且电流增加时二极管两端的电压基本不变,仍等于$V_{ON}$

3.2 TTL门电路

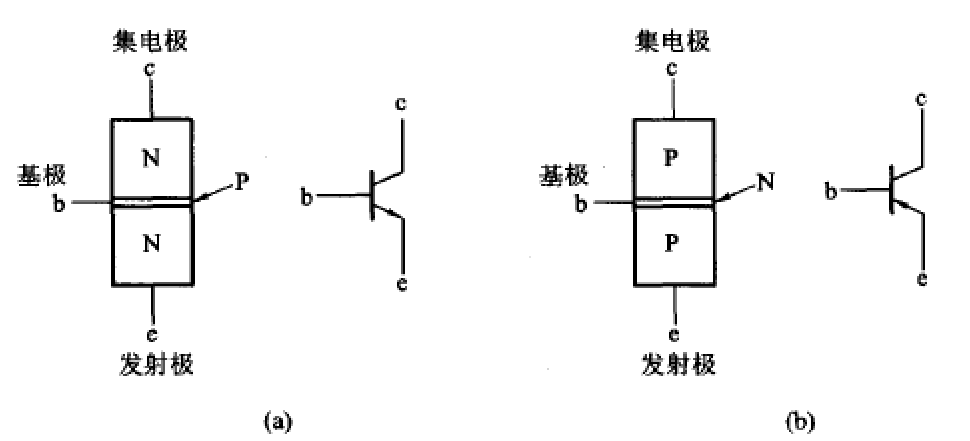

3.2.1 双极型三极管的开关特性

三个电极:基极(base),集电极(collector),发射机(emitter)

两种类型:NPN型和PNP型

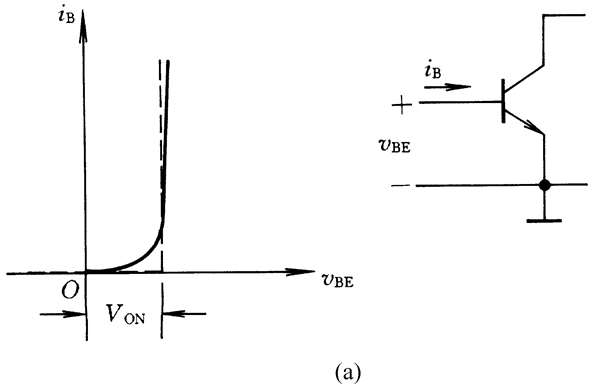

三极管的输入特性和输出特性

$V_{ON}$:开启电压。近似认为:

- $V_{BE}<V_{ON}: i_B=0$

- $V_{BE}\ge V_{ON}: i_B$的大小由外电路电压、电阻决定,$i_B=\frac{V_{BB}-V_{BE}}{R_B}$

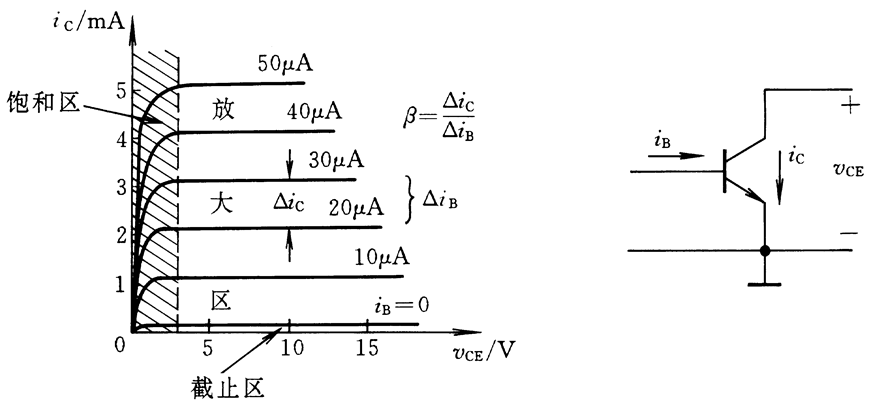

输出特性曲线分为三个部分:

- 放大区:$V_{CE}>0.7V,i_B>0$,$i_C$随$i_B$成正比变化,且几乎不受$v_{CE}$变化影响,$\Delta i_C=\beta\Delta i_B$

- 饱和区:$V_{CE}<0.7V,i_B>0$,$\Delta i_C$随$\Delta i_B$增加变缓,趋于饱和

- 截止区:$V_{BE}=0V,i_B=0,i_C=0$,集电极和发射极之间断开

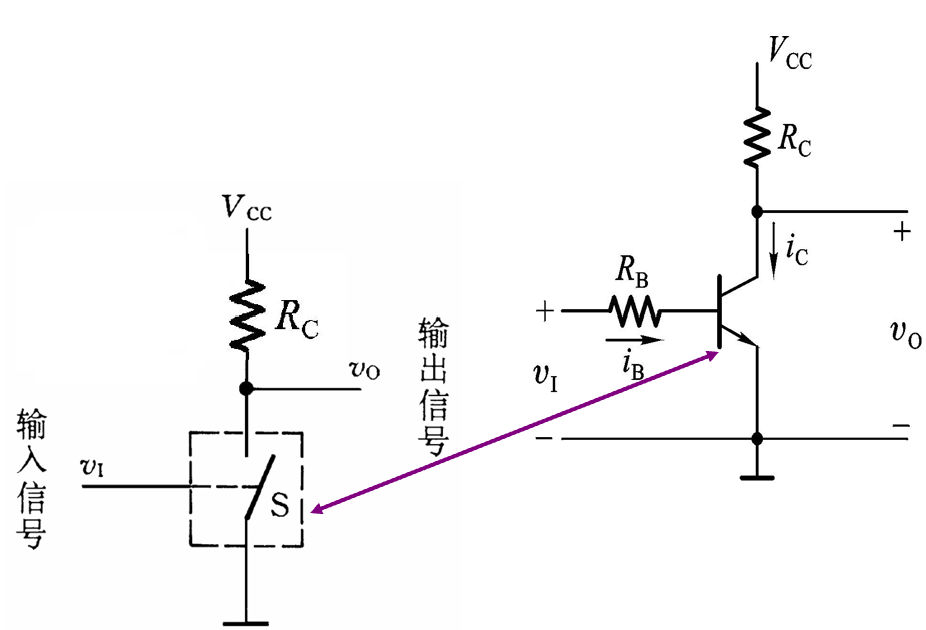

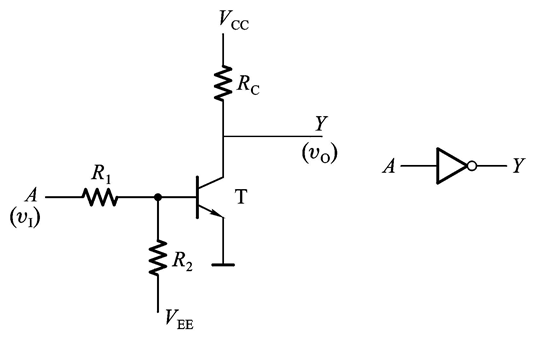

双极型三极管的基本开关电路

适当选择电路参数,使$v_1$为低电平时三极管截止,输出高电平;$v_1$为高电平时三极管饱和,输出低电平。

工作状态分析:

①. 设$V_I=V_{IL}=0$,则$V_{BE}=V_{ON}$,三极管截止,$i_B=i_C$近似为0

②. $V_I$增加至$>V_{ON}$,$i_B=\frac{V_I-V_{ON}}{R_B}> 0$,且有$i_C=\beta i_B$,则$V_O=V_{CE}=V_{CC}-\beta i_BR_C$,三极管工作在放大区

③. $V_I↑→i_B↑→i_C↑→V_O↓$,直至$V_O≈0$,三极管深饱和,$V_O=V_{OL}=V_{CE(sat)}≈0$

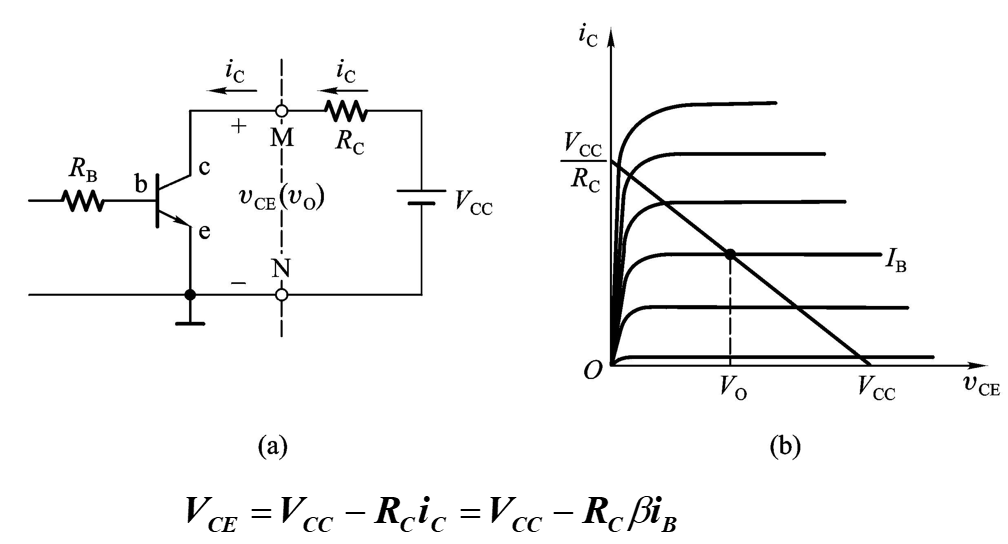

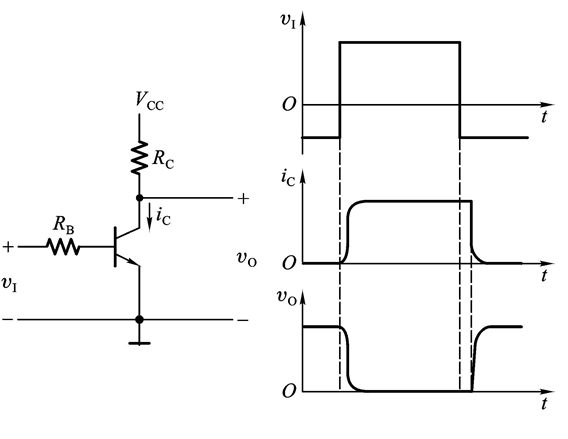

双极性三极管的开关等效电路

$V_{CE(sat)}$和$R_{CE(sat)}$是$c-e$间的饱和导通压降和饱和导通内阻。在电源电压远大于$V_{CE(sat)}$且外接负载电阻远大于$R_{CE(sat)}$的情况下,可将$(b)$简化为$(c)$

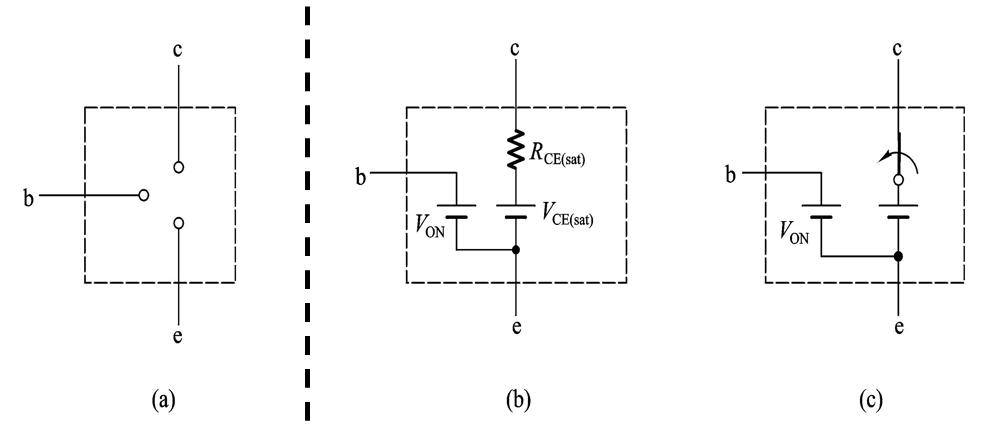

双极性三极管的动态开关特性

$PN$结存在电容效应,在饱和与截止两个状态之间转换时,$i_C$的变化将滞后于$V_I$,则$V_O$的变化也滞后于$V_I$

三极管反相器

上述的三极管开关电路实际上就是一个反向器(非门);在实际中,为保证输入低电平时三极管可靠截止,常在输入接入负压。

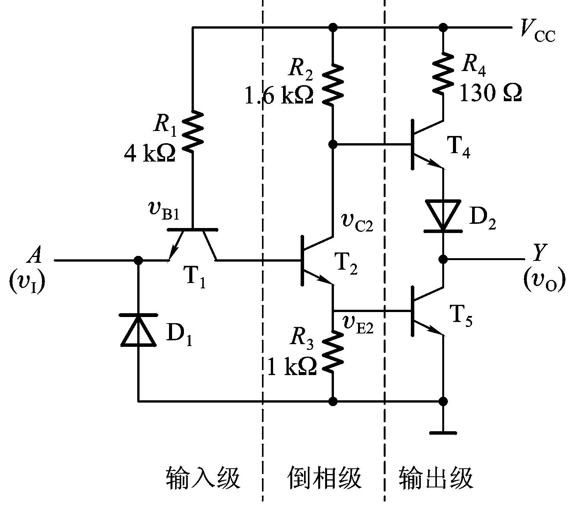

3.2.2 TTL反相器的电路结构和工作原理

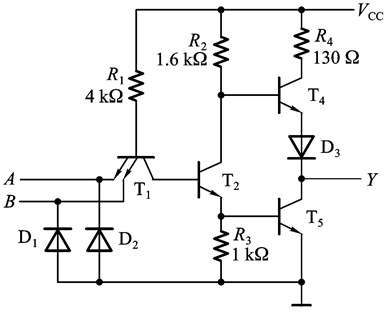

电路结构

$D_1$是输入端钳位二极管,既可以抑制输入负极性干扰脉冲,又可以防止输入电压为负时$T_1$发射极电流过大,起到保护作用。

$D_2$可以保证$T_2$导通时$T_5$可靠地截止。

设$V_{CC}=5V,V_{IH}=3.4V,V_{IL}=0.2V,V_{ON}=0.7V$,

- $V_I=V_{IL}=0.2V(A=0)\Rightarrow V_O=V_{OH}(Y=1)$

- $V_I=V_{IH}=3.4V(A=1)\Rightarrow V_O=V_{OL}(Y=0)$

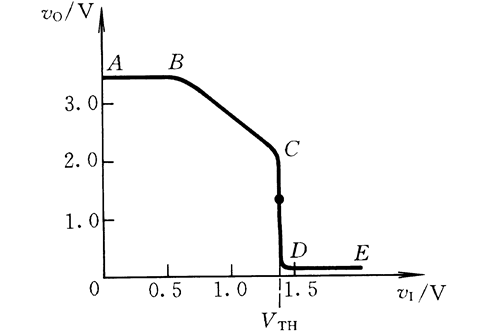

电压传输特性

- $AB$段:截止区,$V_I<0.6V$,则$V_{B1}<1.3V$,$T_1$导通,$T_2,T_5$截止,$T_4$导通$\Rightarrow V_{OH}=V_{CC}-V_{R2}-V_{BE4}-V_{D2}=3.4V$

- $BC$段:线性区,$0.7V<V_1<1.3V$,$T_2$导通且工作在放大区,$T_5$截止,$T_4$导通,$V↑\Rightarrow V_O↓$

- $CD$段:转折区,$V_I=V_{TH}≈1.4V$,则$V_{B1}\ge 2.1V$,$T_2,T_5$同时导通,$T_4$截止,故$V_O$迅速$↓\Rightarrow V_{OL}≈0$

- $DE$段:饱和区,$V_I$继续$↑$,$V_O=V_{OL}$不变

输入噪声容限

在$V_I$偏离$V_{1H}$和$V_{1L}$的一定范围内,$V_O$基本不变。

在输出变化允许范围内,允许输入的变化范围称为输入噪声容限。

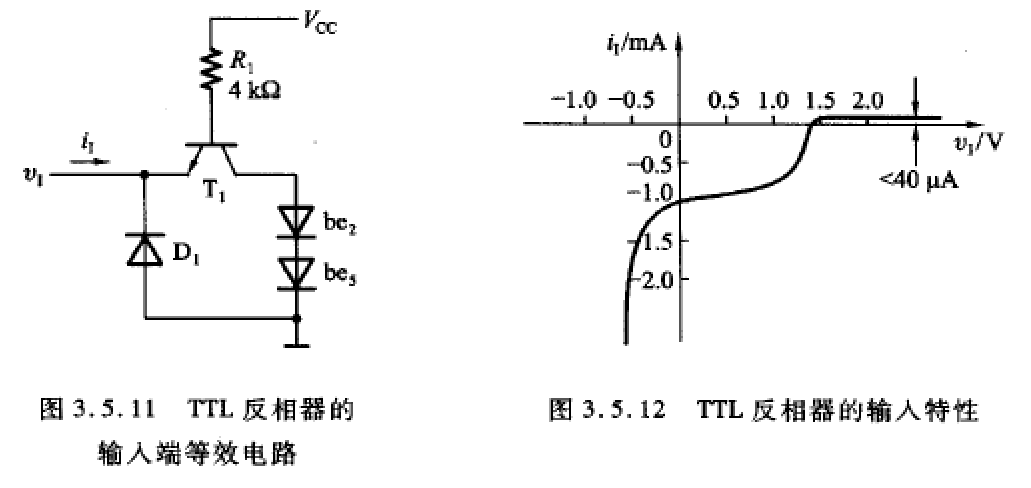

3.2.3 TTL反相器的静态输入特性和输出特性

输入特性

仅仅考虑输入信号是高电平和低电平而不是某一个中间值的情况,则可忽略$T_2$和$T_5$的$b-c$结反向电流以及$R_3$对$T_5$基极回路的影响,输入端等效电路如下:

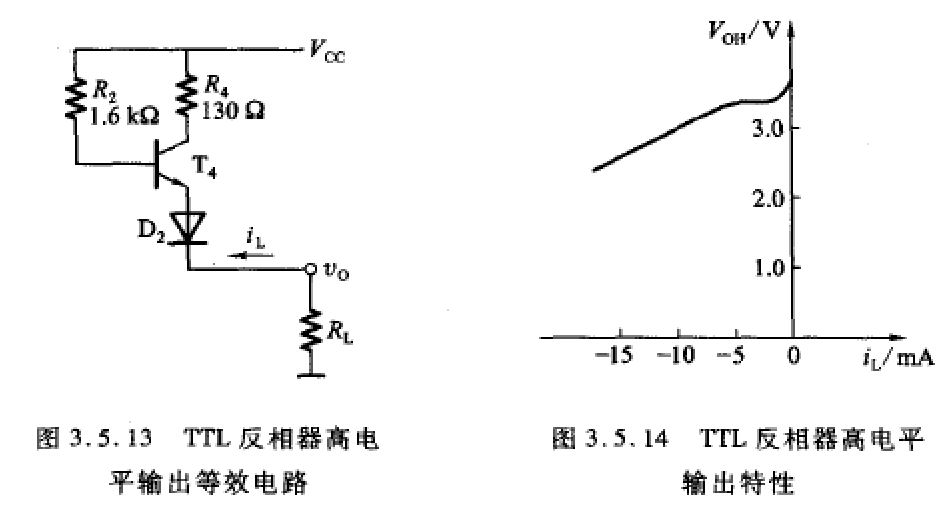

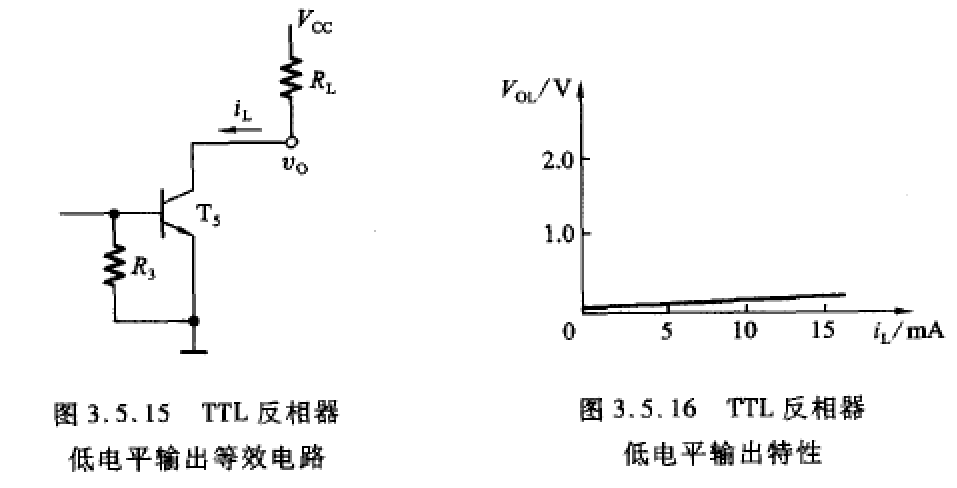

输出特性

3.2.4 TTL反相器的动态特性

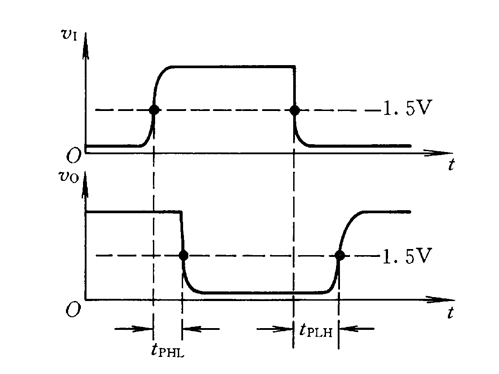

传输延迟时间

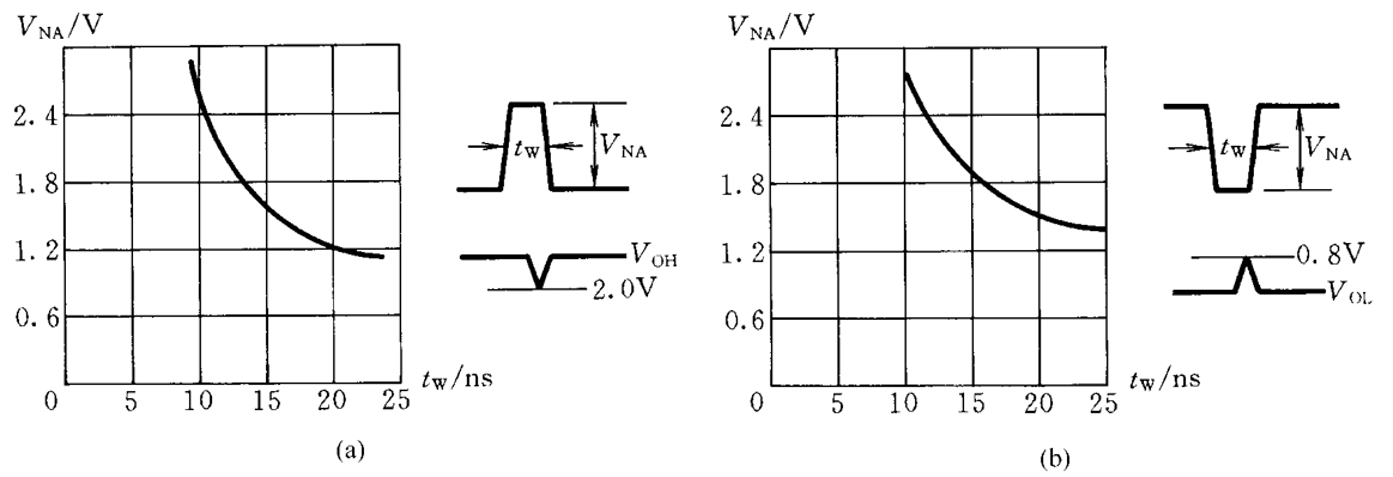

交流噪声容限

$t_w$:输入脉冲宽度;$V_{NA}$:输入脉冲幅度

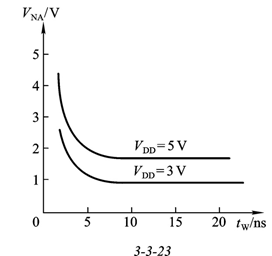

在输入信号为窄脉冲,且脉冲宽度接近门电路传输延迟时间的情况下,输出变化跟不上,变化很小,因此交流噪声容限远大于直流噪声容限。

正脉冲噪声容限:输出高电平由额定值下降至$2.0V$时输入正脉冲的幅度

负脉冲噪声容限:输出低电平由额定值上升至$0.8V$时输入负脉冲的幅度

3.2.5 其它类型的TTL门电路

其它逻辑功能的门电路

虽然他们逻辑功能各异,但输入端、输出端的电路结构形式与反相器基本相同,因此前述反相器的输入特性和输出特性对这些门电路同样适用。

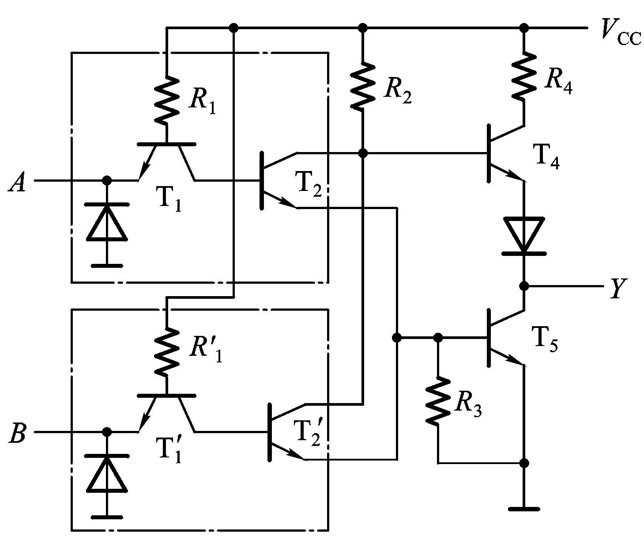

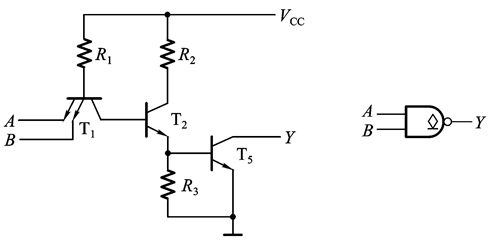

与非门

或非门

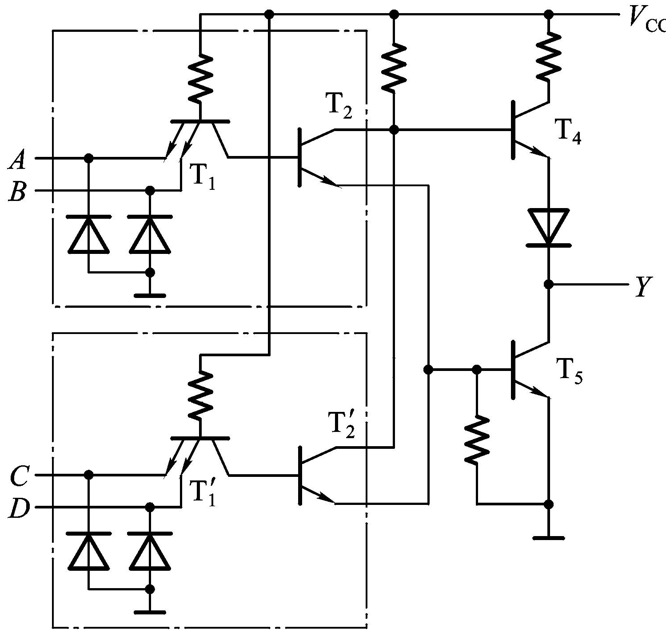

与或非门

异或门

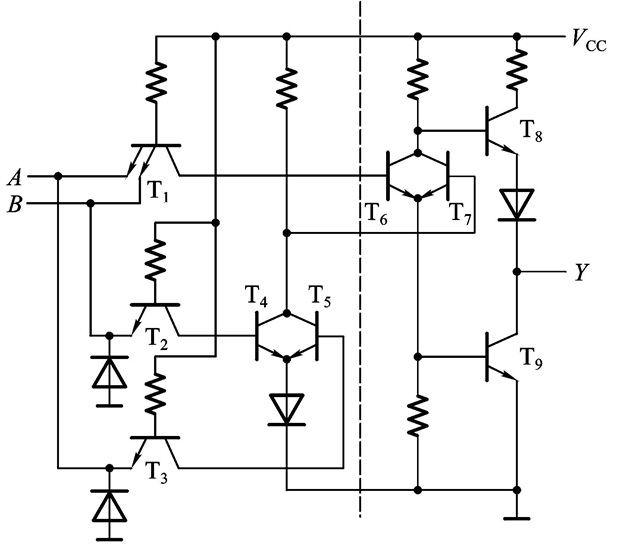

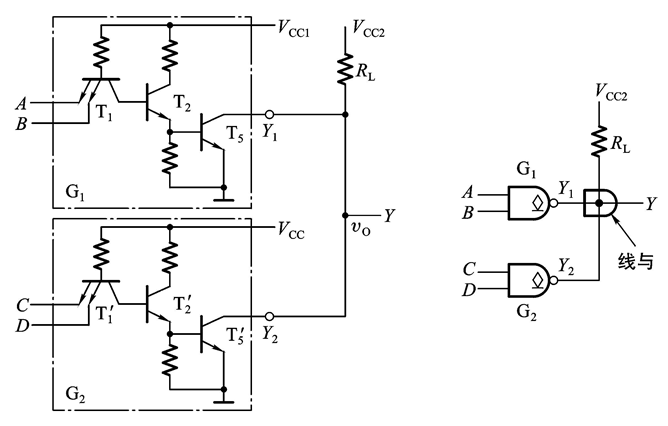

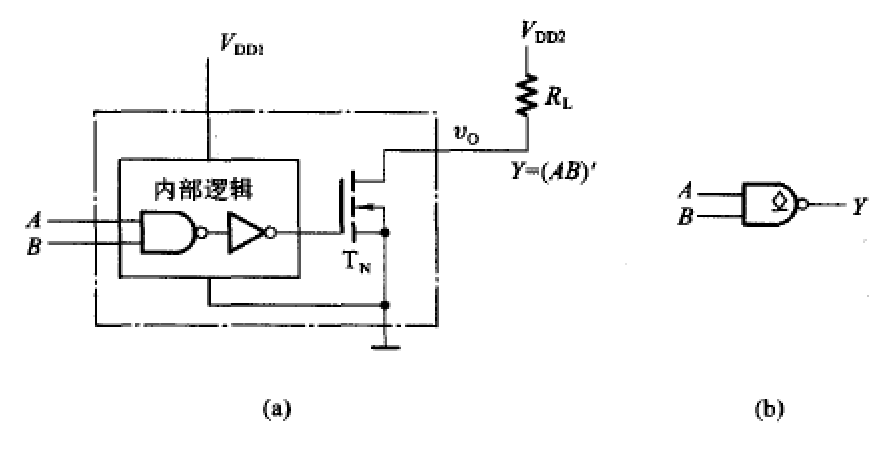

集电极开路输出的门电路(OC门)

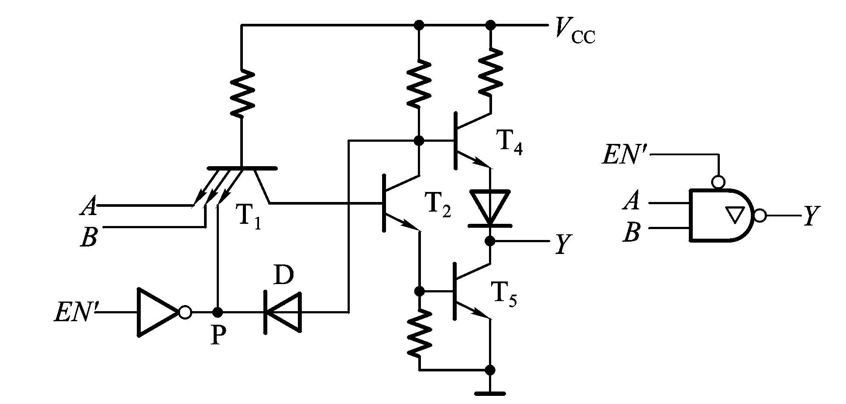

三态输出门电路

输出有三个状态:高电平,低电平,高阻态$(Z)$

- $EN=0,P=1,D$截止,为“工作状态”$\Rightarrow Y=(AB)’$

- $EN=1,P=0,D$导通,为“高阻状态”$\Rightarrow Y=Z$

3.3 CMOS门电路

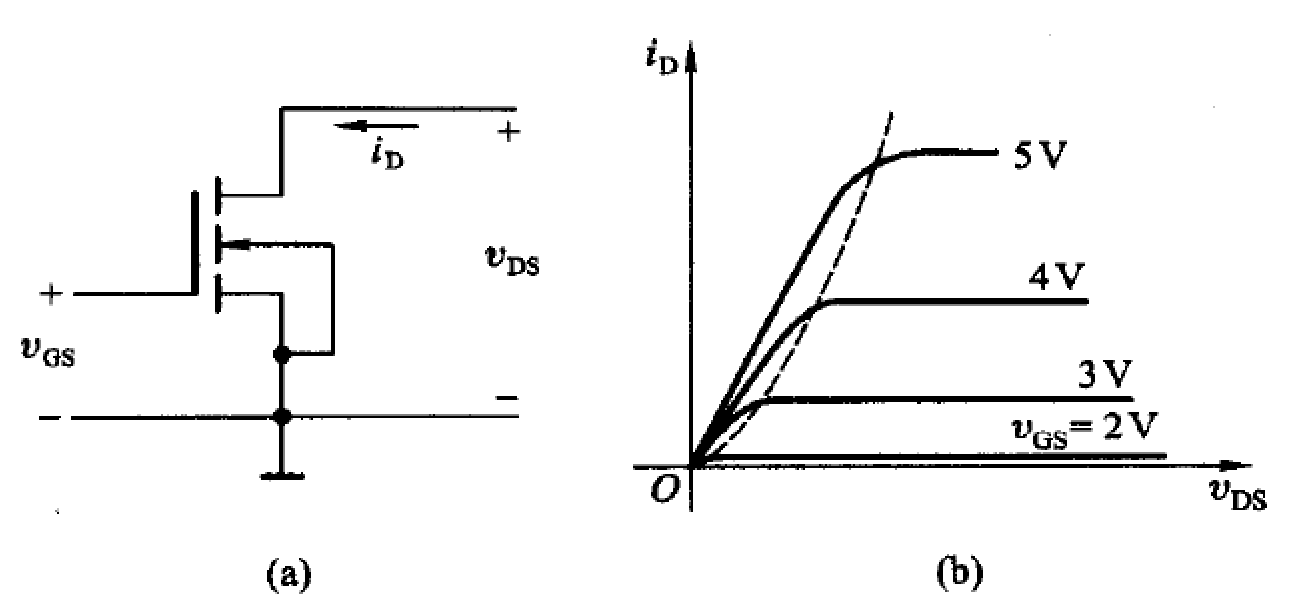

3.3.1 MOS管的开关特性

MOS管的结构

S(Source):源极;G(Gate):栅极;D(Drain):漏极;B:衬底

MOS管的输入特性和输出特性

栅极电流为零,故输入特性曲线无意义。

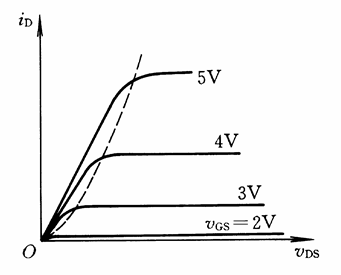

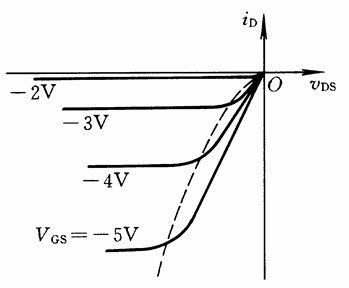

漏极输出特性曲线分为三个工作区:

- 截止区:$v_{GS}<V_{GS(th)}$,漏极和源极间没有导电沟道,$i_d≈0$,$D-S$间的内阻非常大

- 可变电阻区:虚线左边的区域,$v_{DS}/i_D=$常数(电阻),等效电阻的大小和$v_{GS}$的数值有关

- 恒流区:$i_D$由$V_{GS}$决定,与$V_{DS}$关系不大,$i_D=I_{DS}(\frac{V_{GS}}{V_{GS(th)}}-1)^2$

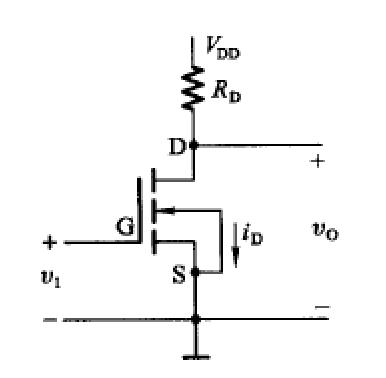

MOS管基本开关电路

MOS管D-S间相当于一个受$V_I$控制的开关:

- 当$V_I=V_{IL}<V_{GS(th)}\to T$截止$\to V_O=V_{OH}≈V_{DD}$

- 当$V_I=V_{IH}>V_{GS(th)}\to T$导通$\to V_O=V_{OL}≈0$

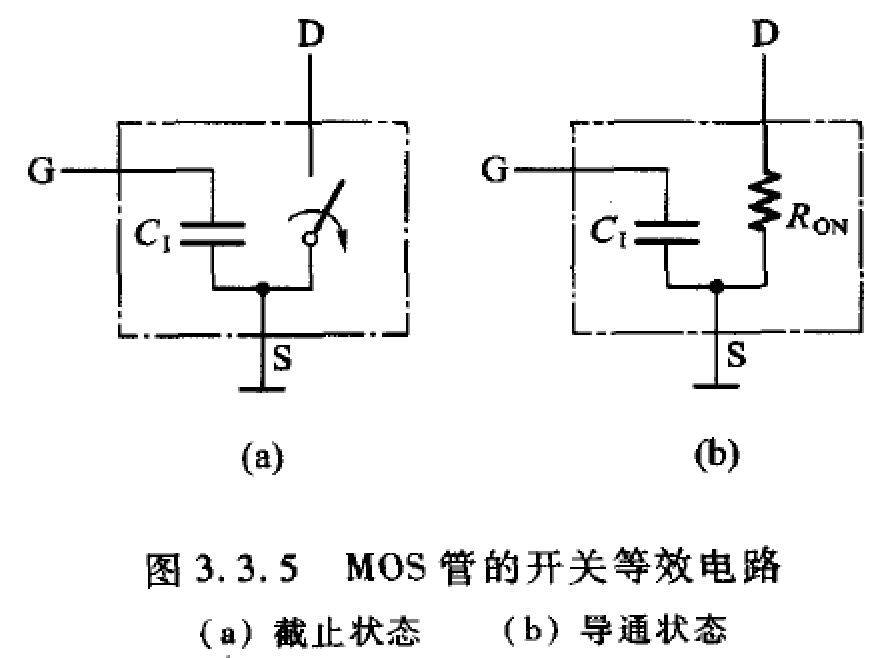

MOS管的开关等效电路

MOS管导通状态下的内阻$R_{ON}$约在$1kΩ$以内,有时不能忽略不计

$C_1$代表栅极的输入电容

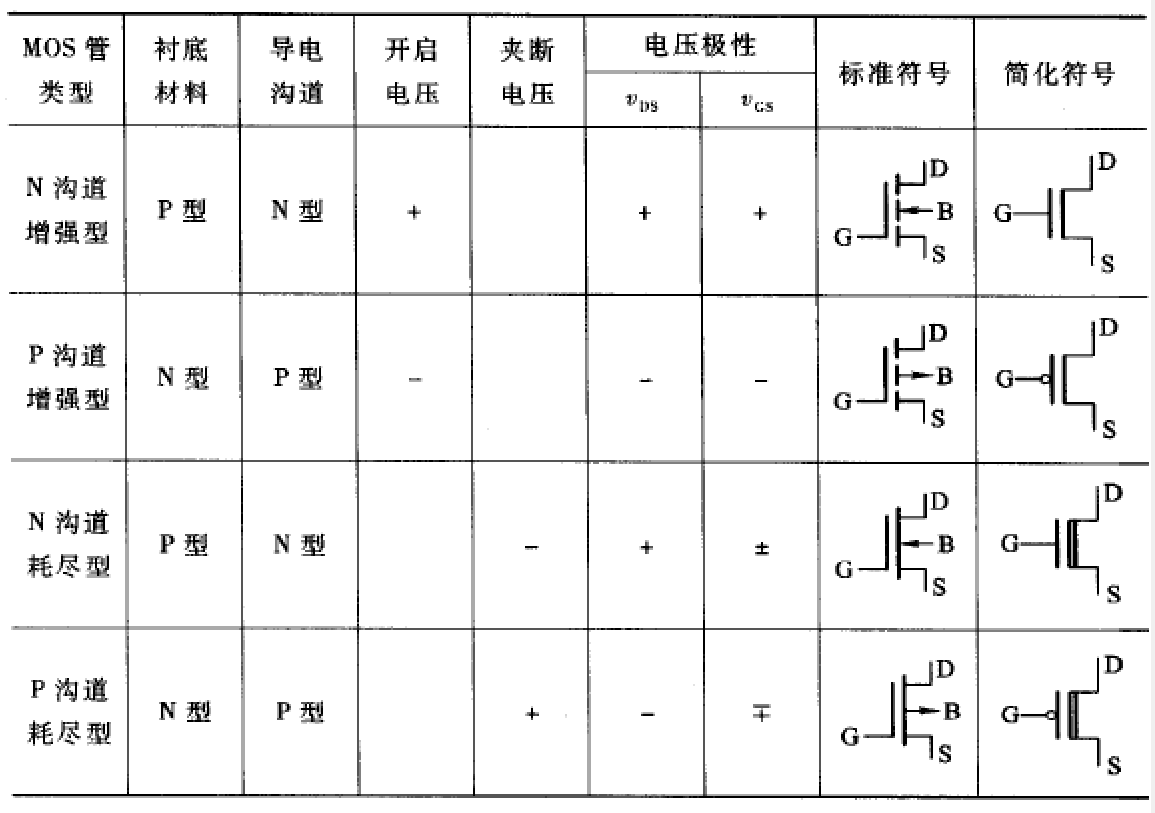

四种类型MOS管

3.3.2 CMOS反相器的电路结构和工作原理

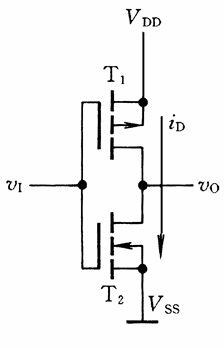

电路结构

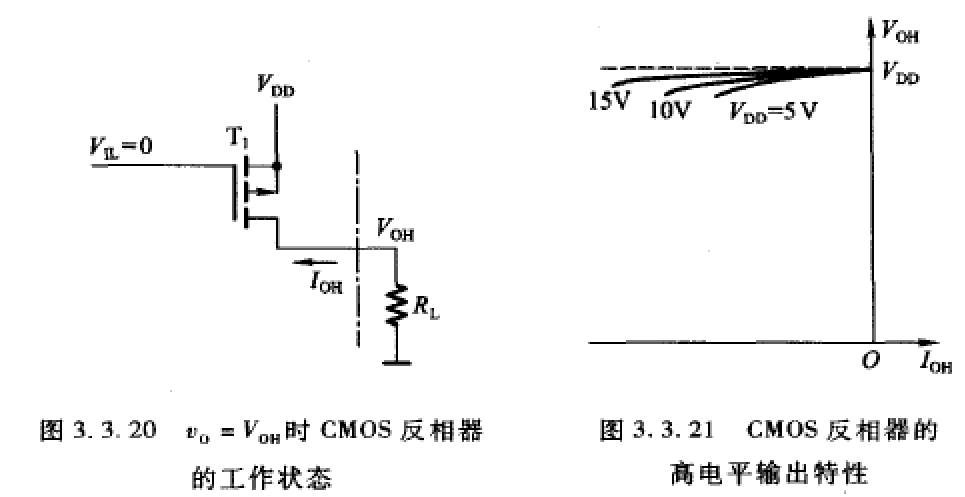

- 当$v_1=V_{IL}=0$时,有$\begin{cases}|v_{GS1}|=V_{DD}>|V_{GS(th)P}|\\ v_{GS2}=0<V_{GS(th)N}\end{cases}$,$T_1$导通,$T_2$截止,输出高电平

- 当$v_1=V_{IH}=V_{DD}$时,有$\begin{cases}v_{GS1}=0<|V_{GS(th)P}|\\ v_{GS2}=V_{DD}>V_{GS(th)N}\end{cases}$,$T_2$导通,$T_1$截止,输出低电平

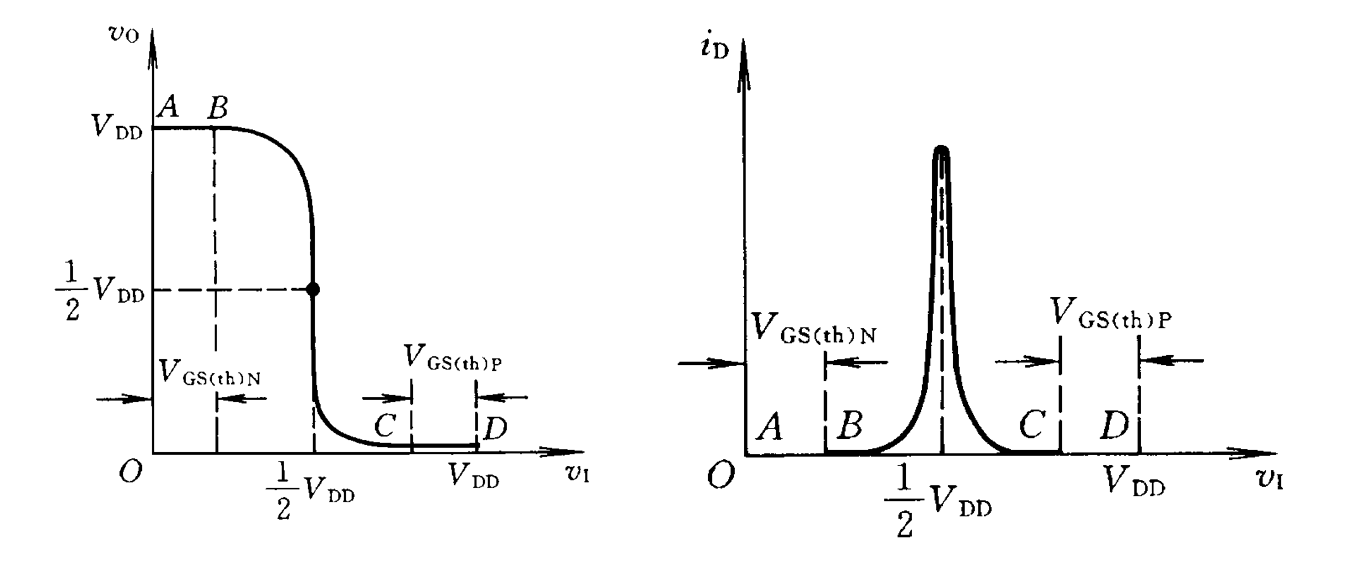

电压和电流传输特性

输入噪声容限

在$V_I$偏离$V_{IH}$和$V_{IL}$的一定范围内,$V_O$基本不变;

在输出变化允许范围内,允许输入的变化范围称为输入噪声容限。

可通过提高$V_{DD}$来提高噪声容限

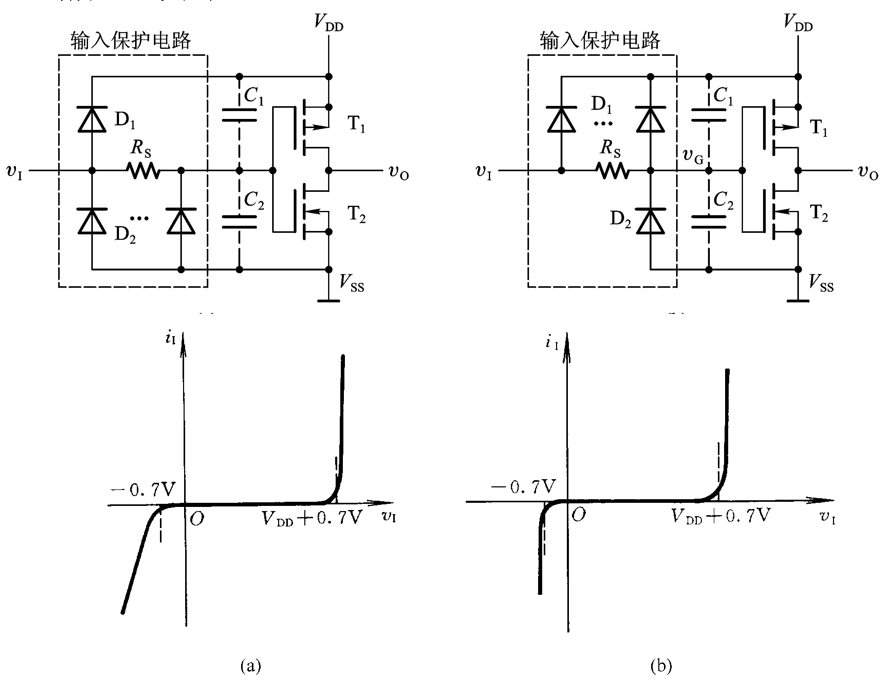

3.3.3 CMOS反相器的静态输入和输出特性

输入特性

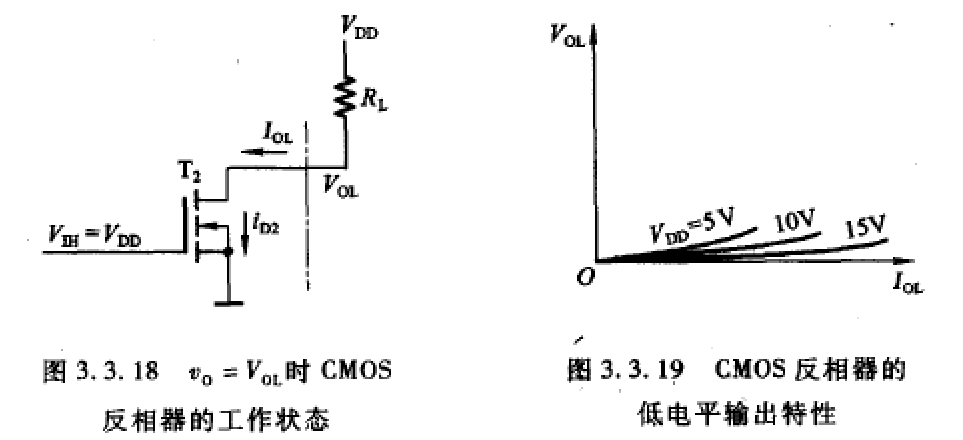

输出特性

由N-MOS输出特性曲线可以看出,同样的$I_{OL}$下,$V_{GS}↑\Rightarrow V_{OL}↓ $

由P-MOS输出特性曲线可以看出,同样的$I_{OL}$下,$V_{GS}↑\Rightarrow V_{OL}$下降的越少

3.3.4 CMOS反相器的动态特性

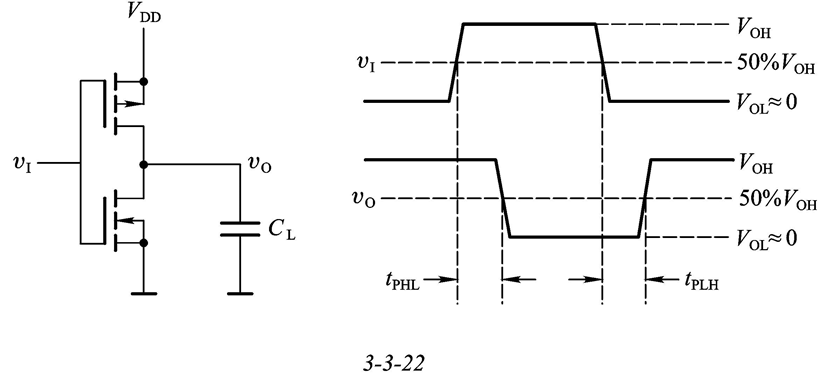

传输延迟时间

输出由低跳至高的传输延迟时间:$t_{PHL}$

输出由高跳至低的传输延迟时间:$t_{PLH}$

CMOS电路的$t_{PHL}=t_{PLH}=t_{pd}$,$t_{pd}$为平均传输延迟时间

交流噪声容限

$V_{NA}$:交流噪声容限;$t_W$:噪声电压的持续时间

动态损耗

当CMOS反相器从一种稳定工作状态突然转变到另一种稳定状态的过程中产生的附加的损耗,称为动态损耗。

动态损耗由两部分组成:对负载电容充、放电所消耗的功率$P_C$,另一部分是由于两个MOS管$T_1$和$T_2$在短时间内同时导通所消耗的瞬时导通功耗$P_T$

课后题(3.5,3.6)涉及的静态功耗、动态功耗和总功耗的计算:

静态功耗:$P_S=I_{DD}V_{DD}$,其中$V_{DD}$是电源电压,$I_{DD}$是静态电源电流

动态功耗:$P_D=(C_L+C_{pd})fV_{DD}^2$,其中$C_L$是负载电容,$C_{pd}$是功耗电容,$f$是输入信号频率

总功耗:$P_{TOT}=P_S+P_D$

电源的平均电流:$\overline I_{DD}=P_{TOT}/V_{DD}$

3.3.5 其它类型的CMOS门电路

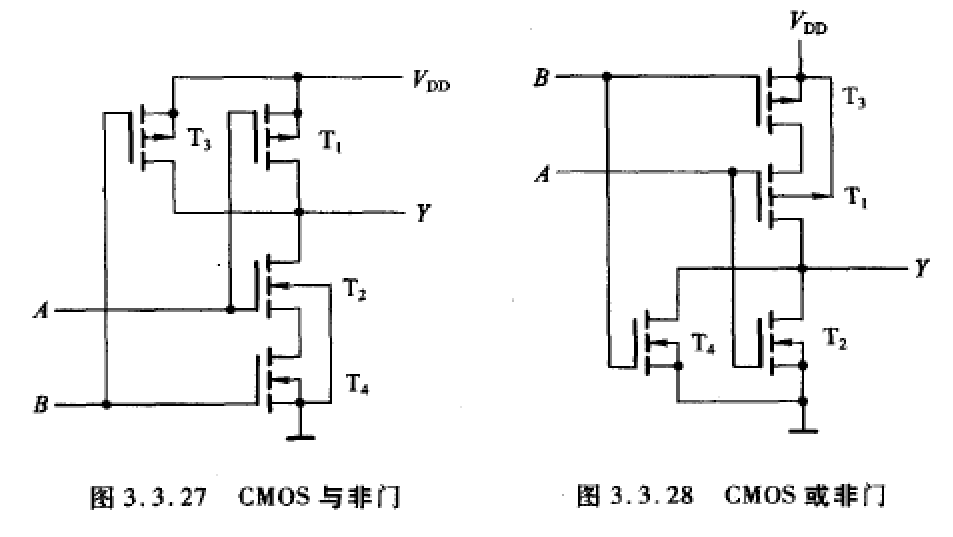

其它逻辑功能的CMOS门电路

漏极开路输出门电路(OD门)

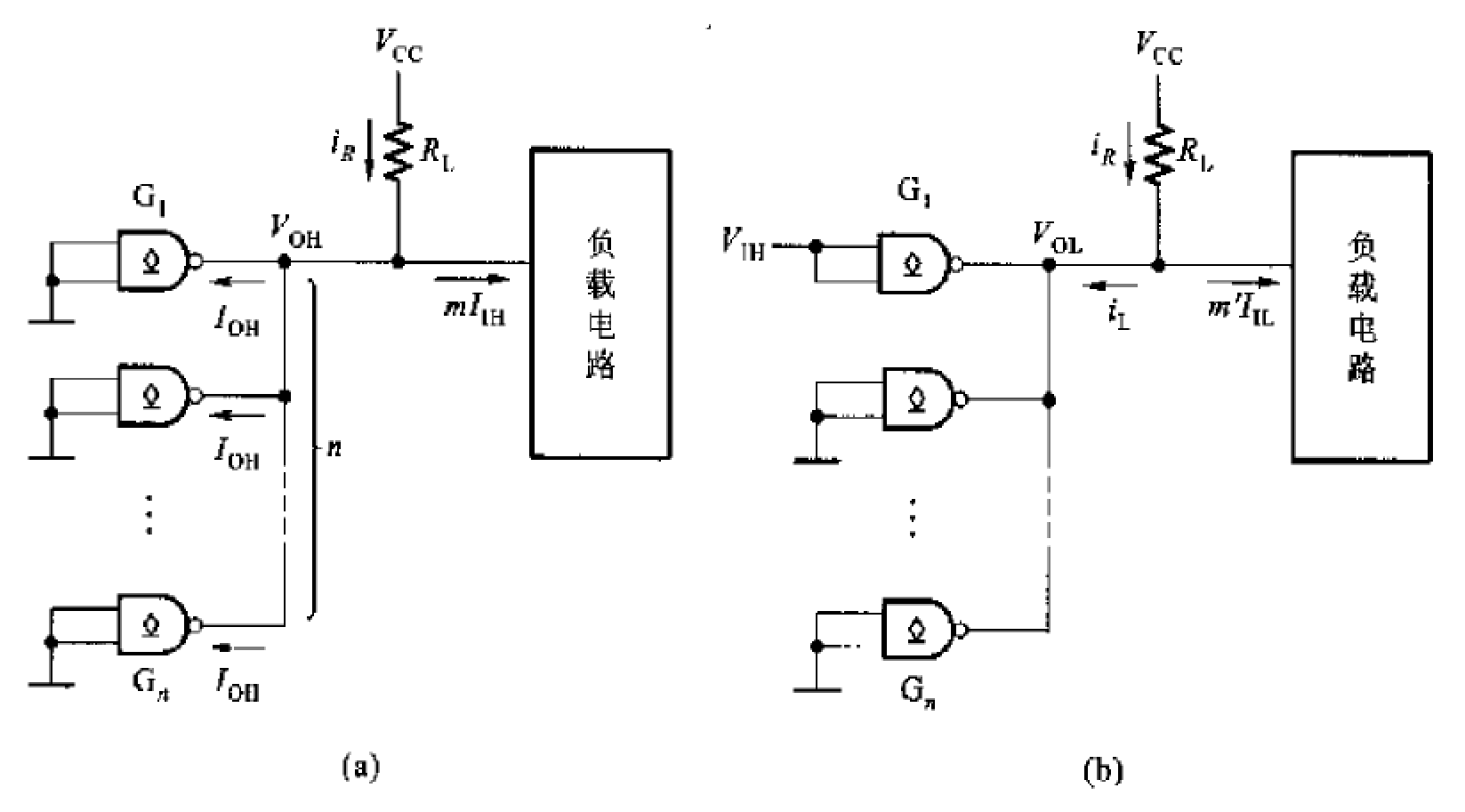

OC门和OD门外接上拉电阻阻值的计算(课后题3.9,3.10,真题考过):

OC门和OD门的应用电路接法可画成下图所示的形式

①. 当OC门(或OD门)全部截止,输出为高时,由图(a),所有OC门输出三极管截止状态下的漏电流$I_{OH}$和负载电路全部的高电平输入电流$\sum I_{IH}$全部流过$R_L$,在$R_L$上产生压降。为保证$v_o$输出的高电平高于要求的$V_{OH}$值,$R_L$的阻值不能取得太大,据此可以求出$R_L$的最大允许值:

上式中的$m$是负载门电路高电平输入电流的数目。

② 当OC门(或OD门)输出为低电平,且只有一个OC门导通时,为保证流过$R_L$的电流和负载电路所有的低电平输入电流全部流入一个导通的OC门时,仍不会超过允许的最大电流$I_{OL(max)}$,$R_L$的阻值不能选得太小。据此可以求出$R_L$的最小允许值:

式中的$V_{OL}$是$OC$门输出三极管的饱和导通压降,$m’$是负载门电路低电平输入电流的数目,负载为$CMOS$门电路时,$m’=m$

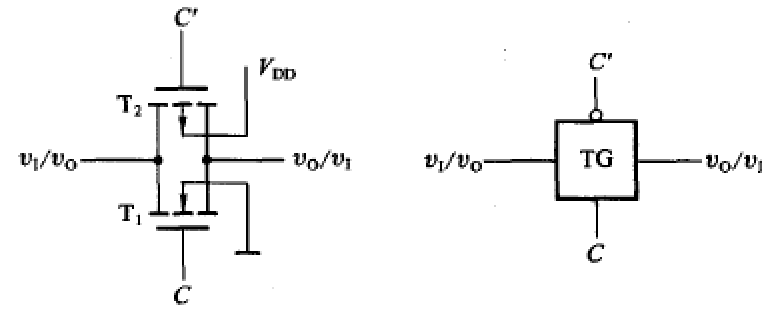

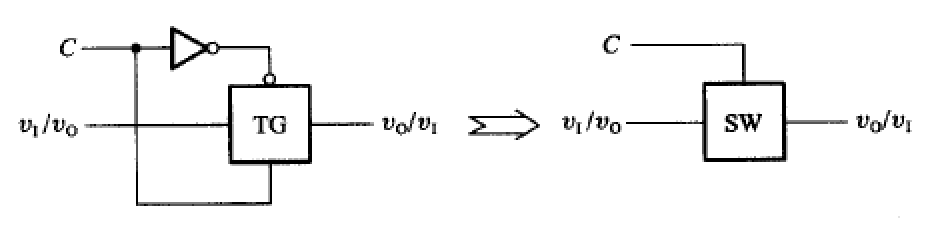

CMOS传输门

设$R_L>>R_{ON},V_{IH}=V_{DD},V_{IL}=0$,

- 当$C=0,C’=1$时,只要$V_1=0\sim V_{DD}$,则$T_1、T_2$均截止,相当于断开

- 当$C=1,C’=0$时,$0<V_I<V_{DD}-V_{GS(th)N}$,$T_1$导通;$|V_{GS(th)P}|<V_I<V_{DD}$,$T_2$导通。即$V_I$在$0\sim V_{DD}$,$T_1、T_2$至少一个导通

传输门的一个重要用途是作模拟开关,用来传输连续变化的模拟电压信号。(这一点是无法用一般的逻辑门实现的)

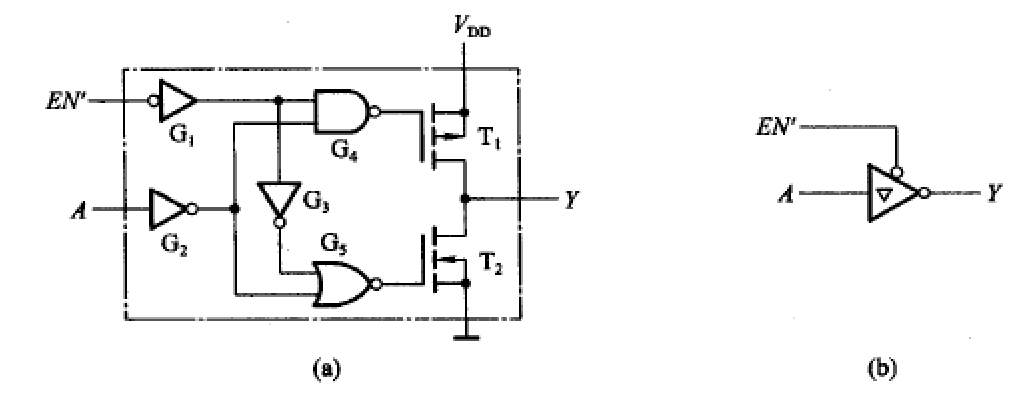

三态输出门

- $EN’=0$时,$Y=A’$

- $EN’=1$时,$Y=Z$(高阻)

3.3.6 CMOS电路的使用注意事项

输入电路的静电防护

①. 不要使用易产生静电高压的化工材料和化纤织物包装,最好采用金属屏蔽层作包装材料;

②. 组装调试时工具应良好接地,操作人员服装原料应是无静电的

③. 不用的输入端不应悬空

输入电路的过流保护

①. 输入端接低内阻信号源时, 应在输入端与信号源之间串进保护电阻

②. 输入端接有大电容时, 亦应在输入端与电容之间接入保护电阻

③. 输入端接长线时,应在门电路的输入端接入保护电阻

注意的点

①. 集成门电路逻辑功能的分析

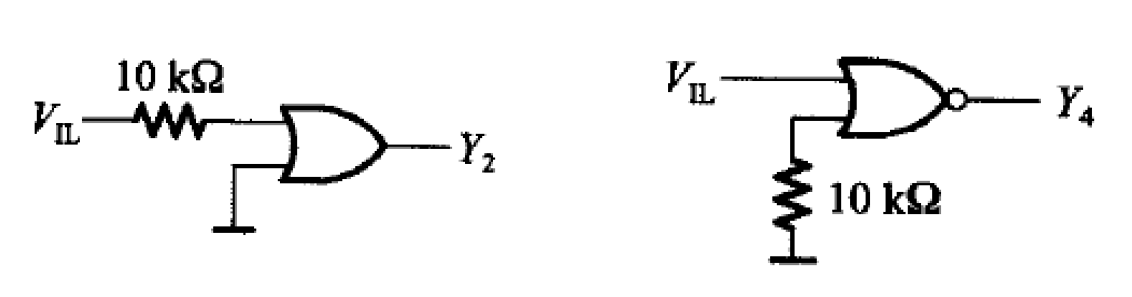

对CMOS门电路而言,通常不允许输入端工作在悬空状态;输入端经电阻接地时,与接逻辑低电平等效;经过电阻接电源电压时,与接逻辑高电平有效。

对TTL门电路而言:

- 输入端的悬空状态和接逻辑高电平等效。

- 输入端经过电阻(通常几十千欧以内)接电源电压时,与接逻辑高电平有效。

- 输入端经过电阻接地时,输入端的电平与电阻阻值的大小有关,

- 当阻值很小时(例如只有几十欧姆),输入端相当于接低电平;

- 当电阻阻值大到一定程度后,输入端电压将升高到逻辑高电平。例如74系列门电路中,当这个电阻大于2kΩ,输入端电压将高于1.4V,这时输入端状态与接逻辑高电平等效。

例如下图左电路输出的是高电平,右电路输出的是低电平。

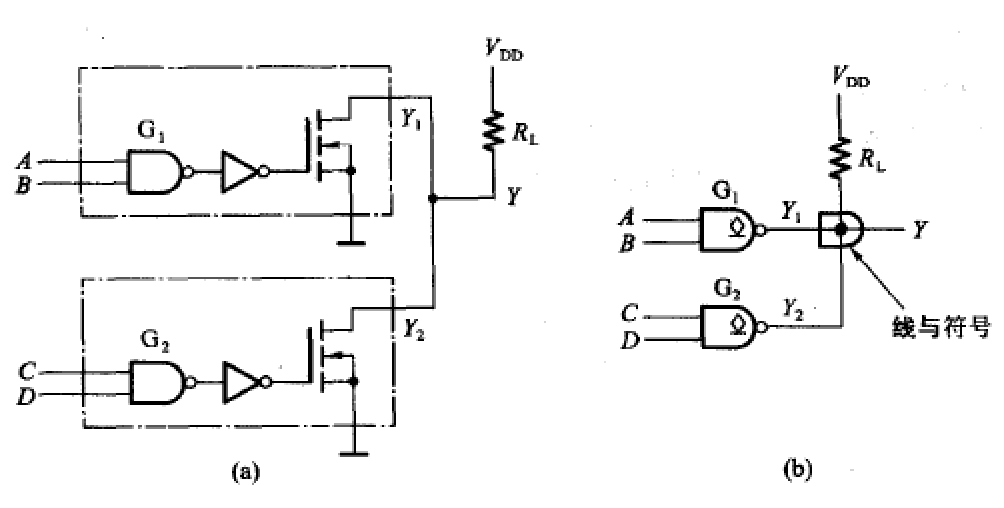

②. 具有推拉式输出级的TTL电路和具有互补输出结构的CMOS的输出不可以并联;TTL电路的OC门和CMOS电路的OD门的输出可以并联实现“线与”;TTL和CMOS电路的三态门的输出可以并联使用,但是应保持任意时刻仅有一个三态门是正常使用,其它均为高阻态。

题型总结