FPGA 第四章:VHDL语言要素

4.1 VHDL文字规则

4.1.1 数字型文字

①. 整数文字:都是十进制的数,加下划线仅仅是为了可读性;

②. 实数文字:也是十进制,但是必须要有小数点;

③. 以数制基数表示的文字。“#”

16#E#E1:16进制的E是十进制中的14,然后E1是指再乘以相应进制数的1次方,即16×14=224。

4.1.2 字符串型文字

①. 文字字符串;

②. 数位字符串:B”1_1101_1110”,O”15”,X”AD”;

③. 标识符:开头必须是英文字符;

④. 下标名:指示数组型变量或信号的某一元素;

标识符(表达式)

例:a(m),b(3)。

⑤. 段名:指示数组型变量或信号的某一段元素;

标识符(表达式 方向 表达式)

4.2 VHDL数据对象

4.2.1 常数$CONSTANT$

CONSTANT 常数名: 数据类型 := 表达式 ;

CONSTANT Vcc : REAL := 5.0 ;

4.2.2 变量$VARIABLE$

适用范围仅限于定义了变量的进程或子程序中。

定义变量:

VARIABLE 变量名: 数据类型 := 初始值 ;

VARIABLE a,b : INERGER := 2 ;

4.2.3 信号$SIGNAL$

是一个全局量。

SIGNAL 信号名: 数据类型 := 初始值 ;

SIGNAL CLK : STD_LOGIC := '1' ;

信号赋值和变量赋值的格式:

信号 <= 表达式;

变量 := 表达式;

4.3 VHDL数据类型

4.3.1 VHDL预定义数据类型

只列出几个重要的:

①. 布尔$BOOLEAN$:

在程序包STANDARD中定义的源代码为:

TYPE BOOLEAN IS (FALSE, TRUE) ;

②. 位$BIT$:

在程序包STANDARD中定义的源代码为:

TYPE BIT IS ('0','1') ;

③. 位矢量$BIT\underline \ VECTOR$:

使用:

SIGNAL a : BIT_VECTOR(7 TO 0) ;

④. 整数$INTEGER$:

使用:

SIGNAL typei : INTEGER RANGE 0 TO 15 ;

4.3.2 IEEE预定义标准逻辑位与矢量

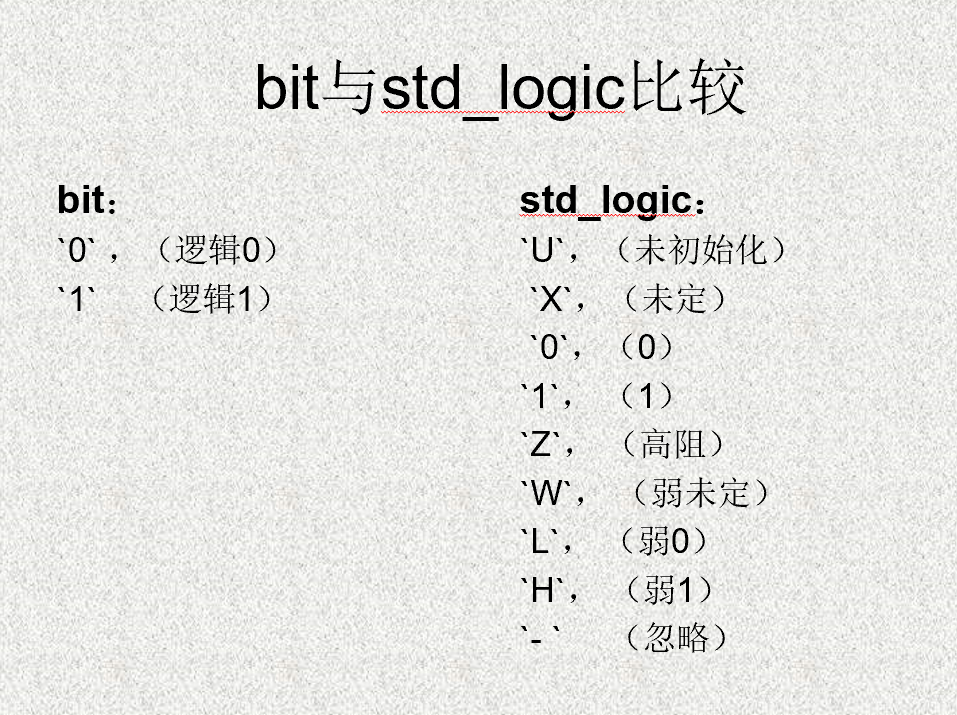

①. 标准逻辑位$STD\underline \ LOGIC$

②. 标准逻辑矢量$STD\underline \ LOGIC\underline \ VECTOR$

4.3.4 用户自定义数据类型方式

①. $TYPE$语句用法

TYPE 类型名 IS 类型定义 ;

例:

TYPE byte IS ARRAY(7 DOWNTO 0) of BIT ;

VARIABLE v1 : byte ; --v1的数据类型定义为byte

②. $SUBTYPE$语句用法

子类型的定义只在基本数据类型上做一些约束,并没有定义新的数据类型。

SUBTYPE 子类型名 IS 基本数据类型 RANGE 约束范围

枚举类型

用文字表示一组二进制数据。

例:

TYPE my_logic IS ('1','Z','U','0') ;

SIGNAL S1 : mylogic ;

S1 <= 'z' ; < code>整数和实数类型

限定范围的整数和实数。

TYPE 类型名 IS 限定范围描述 ;

TYPE percent IS RANGE -100 TO 100 ;

数组类型

用于定义同一类型值的集合。

TYPE 类型名 IS ARRAY 范围 OF 原数据类型名

TYPE WORD IS ARRAY (31 DOWNTO 0) OF BIT ;

记录类型

用于定义不用类型值的集合。

TYPE 记录类型名 IS RECORD

元素名 : 元素数据类型 ;

元素名 : 元素数据类型 ;

...

END RECORD 记录类型名 ;

数据类型转换

①. 直接类型转换方式

VARIABLE X : INTEGER ; VARIABLE Y : REAL ;

X := (INTEGER)Y; Y := (REAL)X;

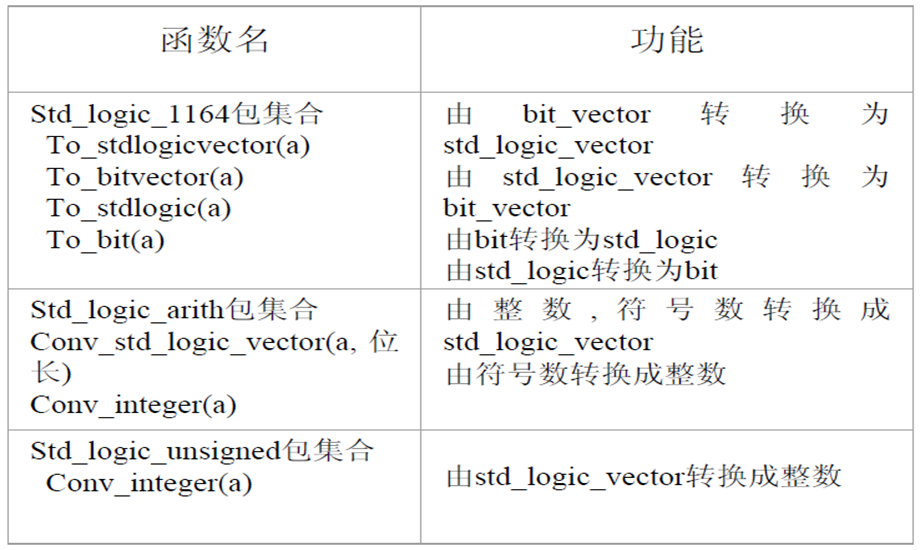

②. 类型函数转换方式

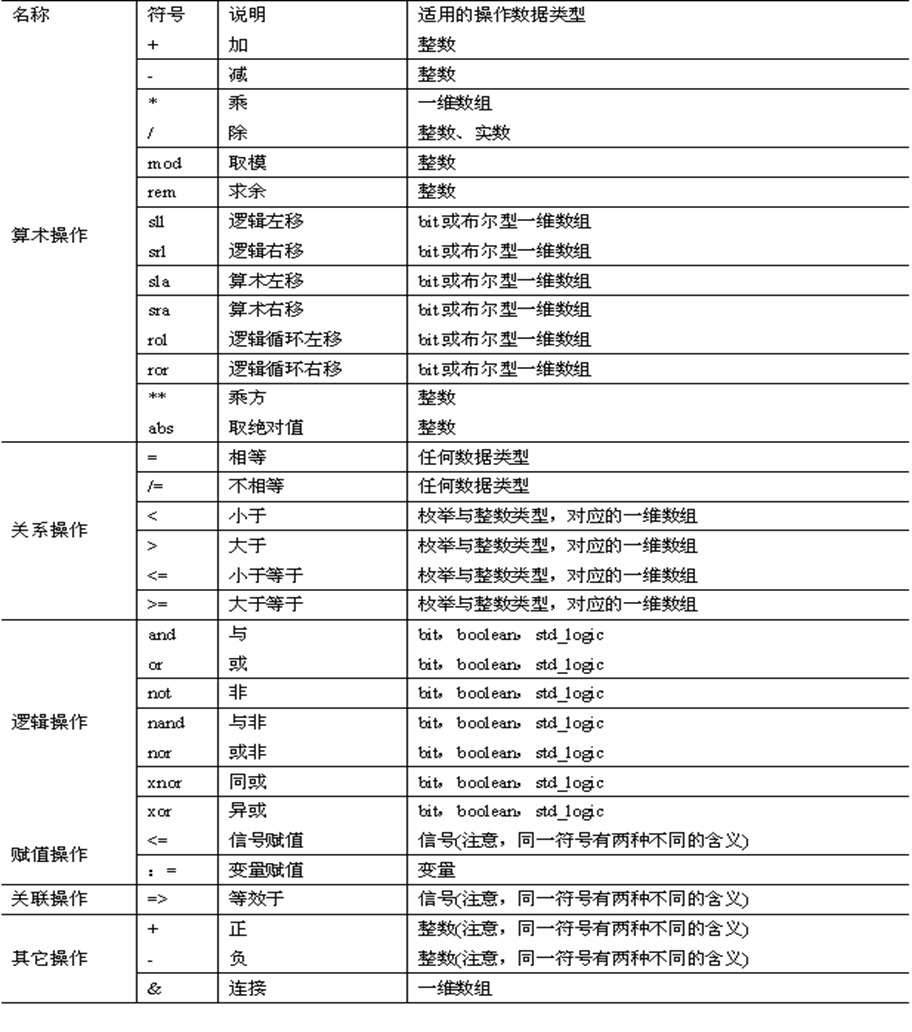

4.4 VHDL操作符