FPGA 第零章 PLD发展概述

超大规模继承电路设计方法

①. 层次化设计

②. 自顶向下的设计

FPGA基本结构

FPGA由可编程逻辑块(CLB)、输入/输出模块(10B)及可编程互连资源(PIR)等三种可编程电路和一个SRAM结构的配置存储单元组成。

①. 可编程逻辑块(CLB):主要由逻辑函数发生器、触发器、数据选择器等电路组成。

②. 输入/输出模块(IOB):主要由输入触发器、输入缓冲器和输出除法/锁存器、输出缓冲器组成,每个IOB控制一个引脚,它们可被配置为输入、输出或双向I/O功能。

③. 可编程互连资源(PIR):由许多金属线段构成,这些金属线段带有可编程开关,通过自动布线实现各种电路的连接。实现FPGA内部的CLB和CLB之间、CLB和IOB之间的连接。

CPLD:MAX7000系列

主要包括:

①. 逻辑阵列块;

②. 宏单元;

③. 扩展/并行乘积项;

④. 可编程连线阵列;

⑤. IO控制块。

PLD设计

| 特性 | CPLD(复杂可编程逻辑器件) | FPGA(现场可编程逻辑门阵列) |

|---|---|---|

| 结构工艺 | 乘积项结构 | 查找表加寄存器结构 |

| 触发器量 | 少 | 多 |

| 规模和复杂度 | 规模小,复杂度低 | 规模大,复杂度高 |

| 时延 | Pin-Pin延时固定 | Pin-Pin延时不可预测 |

| 编程灵活性 | 灵活性小 | 灵活性大 |

| 功耗 | 大 | 小 |

| 编程方式 | 基于EEPROM或者FLASH编程,掉电信息不丢失 | 基于SRAM编程,掉电信息丢失 |

| 保密性 | 好 | 差 |

| 成本 | 低 | 高 |

一些名词解释

①.VHDL:超高速集成电路硬件描述语言

Very-High-Speed Integrated Circuit Hardware Description Language

②. FPGA:现场可编程逻辑门阵列

Field-Programmable Gate Array

③. RTL:寄存器传输级

Register-Transfer Level

④. SOPC:可编程片上系统

System-on-a-Programmable-Chip

⑤. EAB:嵌入式阵列块

Embedded Array Block

⑥. LAB:逻辑阵列块

Logic Array Block

⑦. EDA:电子设计自动化

Electronic Design Automation

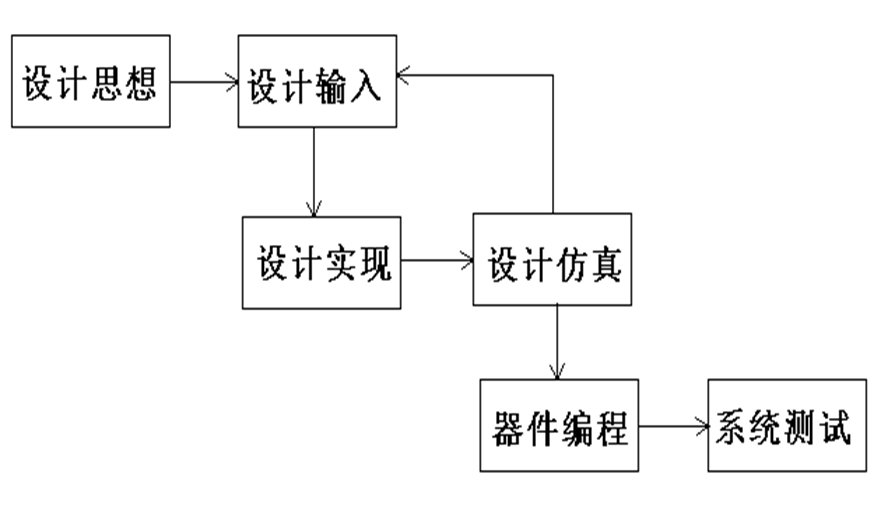

PLD设计流程

设计输入:原理图输入、状态图输入、波形图输入和HDL文本输入

EDA工具组成

①. 仿真器(Simulator)

②. 综合器(Synthesizer)

③. 配置器(Place and Routing,P&R)