用编码器和计数器设计可控分频器

05年真题

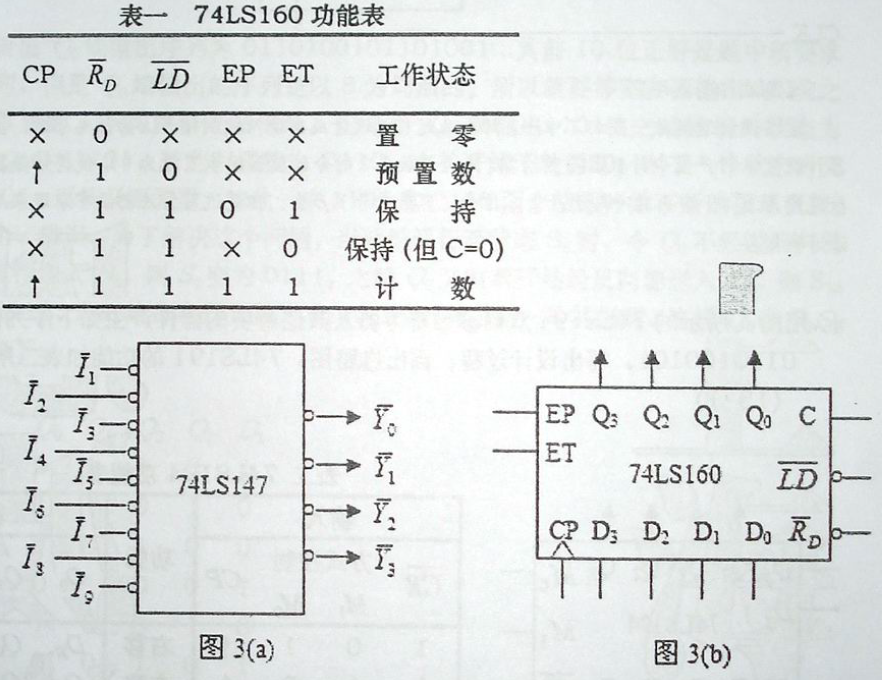

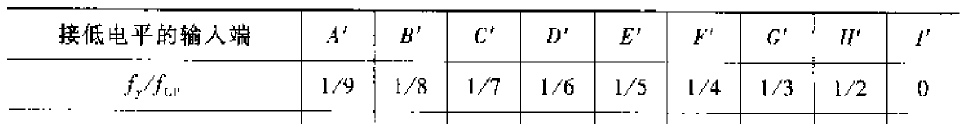

九、用2-10进制优先编码器74LS147和同步十进制计数器74LS160及其它必要的器件组成可控分频器,当输入控制信号A、B、C、D、E、F、G、H分别为低电平时,输出脉冲与时钟脉冲的分频比分别为1/9、1/8、1/7、1/6、1/5、1/4、1/3、1/2.

设计思路:当输入控制信号A,为低电平时,输出脉冲与时钟脉冲的分频比为1/9,我们可以在计数器输出9的时候将其置数为1,即1~9循环,从而实现1/9的分频。

- 因为同步十进制计数器是输出为9时进位输出位C为1,所以可以直接将C反接作为置数的输入。

- 然后将$A$作为优先编码器的$\bar I_1$的输入,这样当$A$为低电平时,编码器输出$\bar Y_3\bar Y_2\bar Y_1\bar Y_0=1110$

- 此时为了让计数器的输入为$0001$,将$\bar Y_3\bar Y_2\bar Y_1\bar Y_0$反接作为$D_3D_2D_1D_0$的输入。

相关课本课后题

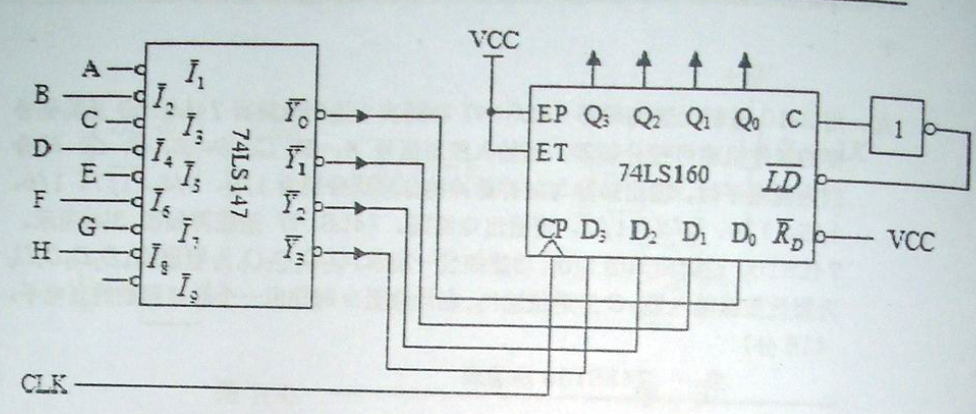

6.24 下图是用二-十进制优先编码器$74LS147$和同步十进制计数器$74160$组成的可控分频器,求各种输入控制情况下的分频比。

解:当$C=1$时($Q_3Q_2Q_1Q_0=1001$时),下一个$CLK$上升沿计数器置入编码器的输出状态$Y_3Y_2Y_1Y_0$.

$A’=0$时$\bar Y_3\bar Y_2\bar Y_1\bar Y_0=1110$,$D_3D_2D_1D_0=0001$,此时计数器的计数循环为$0001\sim 1001$,分频比为$1/9$。其它输入控制状态同理。

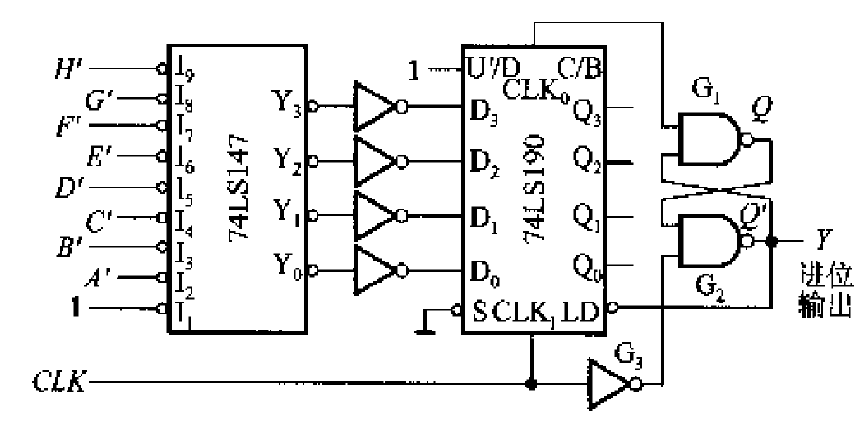

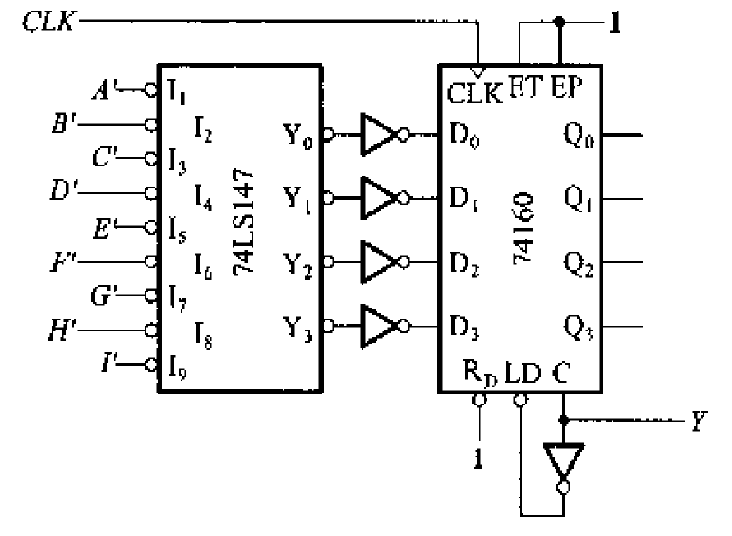

6.25 用同步十进制可逆计数器74LS190和二-十进制优先编码器74LS147设计一个工作在减法器级数状态的可控分频器。要求在控制信号A、B、C、D、E、F、G、H分别为1时分频比对应为1/2、1/3、1/4、1/5、1/6、1/7、1/8、1/9.

思路:

- $CLK_0$可作为$LD’$信号,因为在$CLK$上升沿使得$Q_3Q_2Q_1Q_0=0000$以后,在这个$CLK$的低电平期间$CLK_0$将给出一个负脉冲。

- $74LS190$是异步置数,所以$0000$不是计数循环里的状态,所以控制信号$A$起作用时,需要置数为$0010$,此时计数循环为$2\sim1$,分频比为$1/2$,所以把$A$反接在$\bar I_2$处,再把编码器的输入$\bar Y_3\bar Y_2\bar Y_1\bar Y_0$反接作为计数器的输入$D_3D_2D_1D_0$,$\bar I_1$接高电平,这样当$A=1$时可有$D_3D_2D_1D_0=0010$。

- 又为了提高置数的可靠性,并产生足够宽度的进位输出脉冲,可以增设由$G_1、G_2$组成的锁存器,由$Q’$端给出与$CLK$脉冲的低电平等宽的$LD’=0$信号,并可由$Q’$端给出进位输出脉冲。