用集成计数器设计任意进制计数器

04年真题

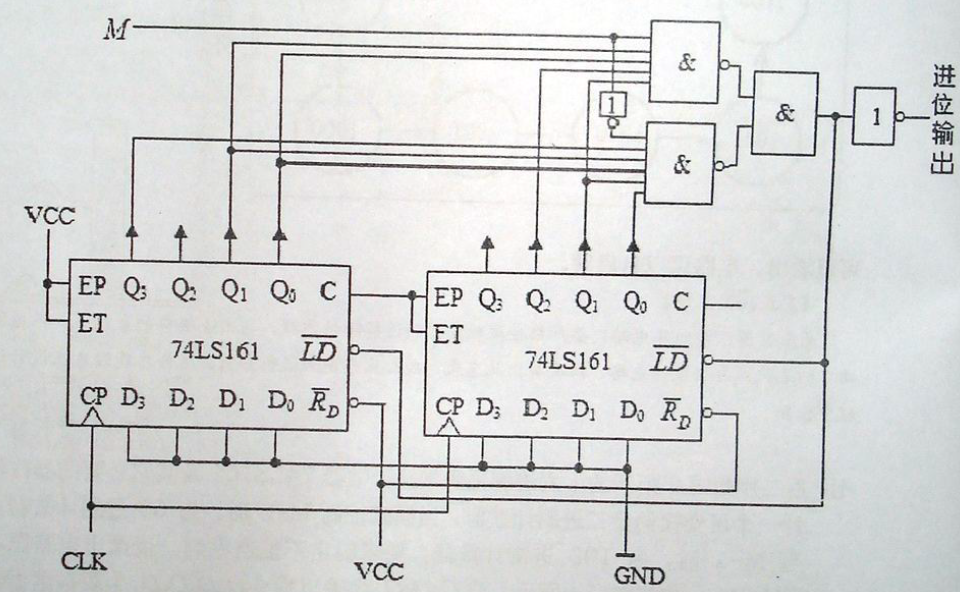

七、用2片十六进制同步加法计数器74LS161及其他必要的器件设计一个可变模同步二进制计数器,当模式控制M=0时为60进制计数器,当M=1时为100进制计数器。要求输出不能由毛刺。

思路:

- $M=0$时,因为是同步,所以计数循环为$0\sim 59$。$3×16+12=60$,所以两个计数器的计数循环为$0000\ 0000\sim 0011\ 1011$;同理$M=1$时,$6×16+4=100$,计数循环为$0000\ 0000\sim 0110\ 0011$。

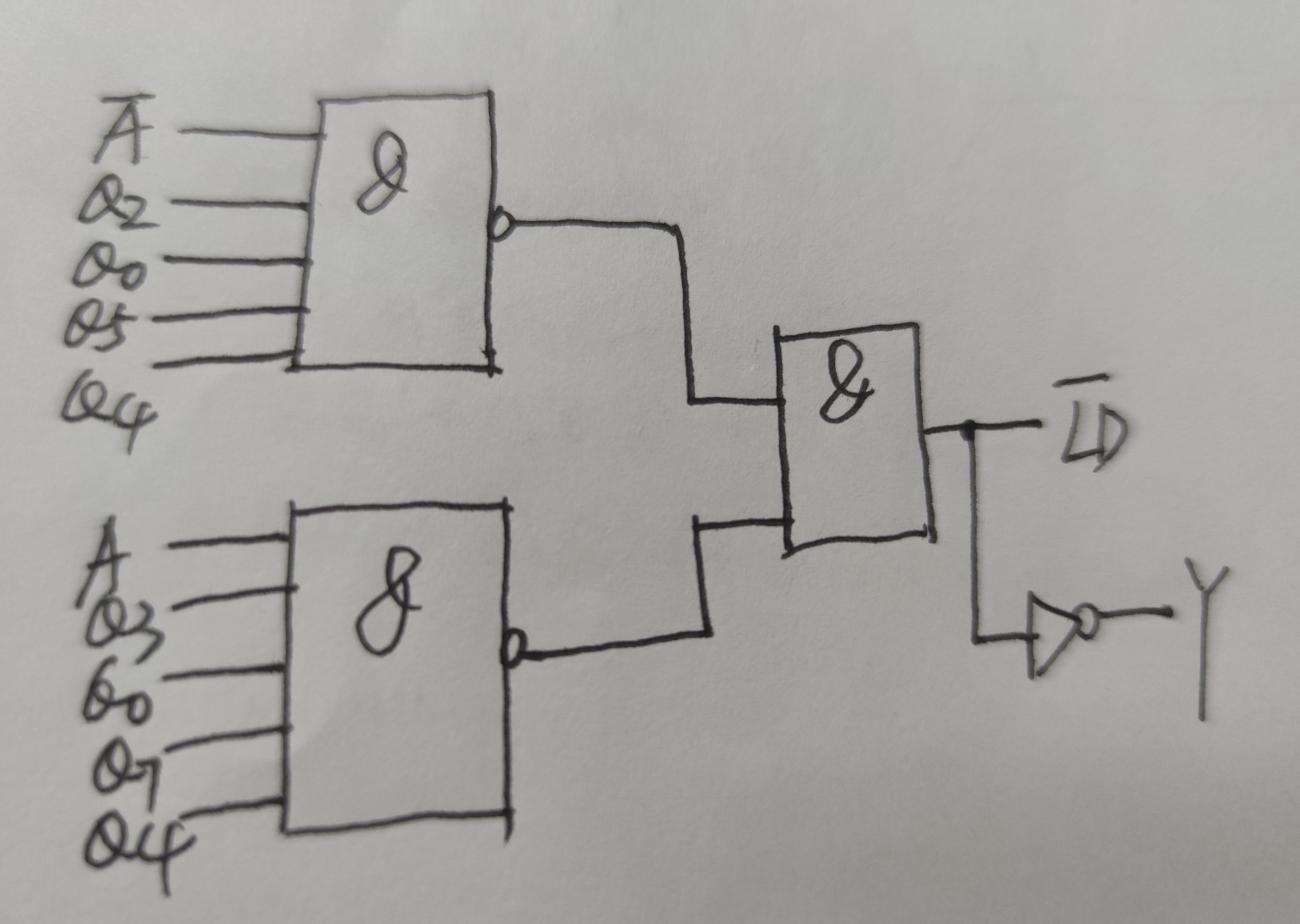

- 可以采用整体置数法,(因为置零是异步,所以不能直接用整体置零,输出会产生毛刺;但是应该可以接一个SR锁存器,在此暂时不再讨论),置数信号为$\overline {LD}=\overline{\overline M\cdot Q_{13}Q_{11}Q_{10}\cdot Q_{21}Q_{20}}\cdot \overline{M\cdot Q_{11}Q_{10}\cdot Q_{22}Q_{21}}$。

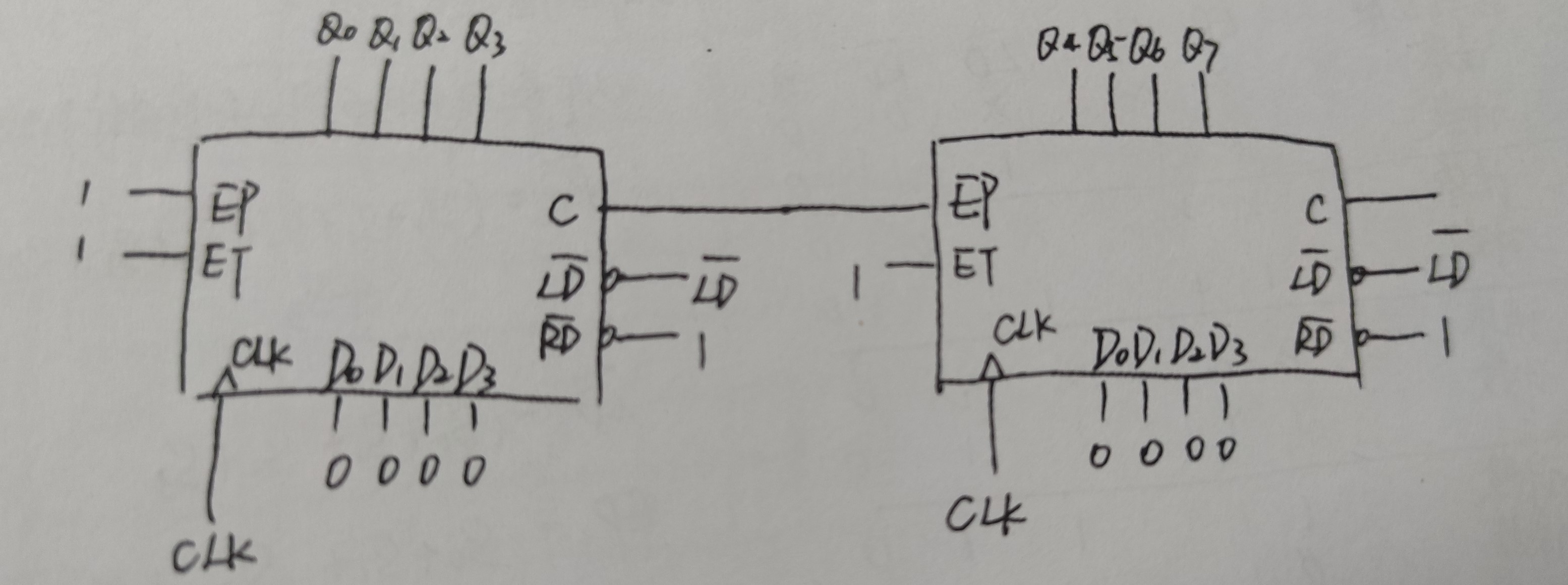

- 电路图如下,需要注意,需要将$\overline {LD}$的输入取反得到进位输出,$C=\overline{\overline {LD}}$。

07年真题

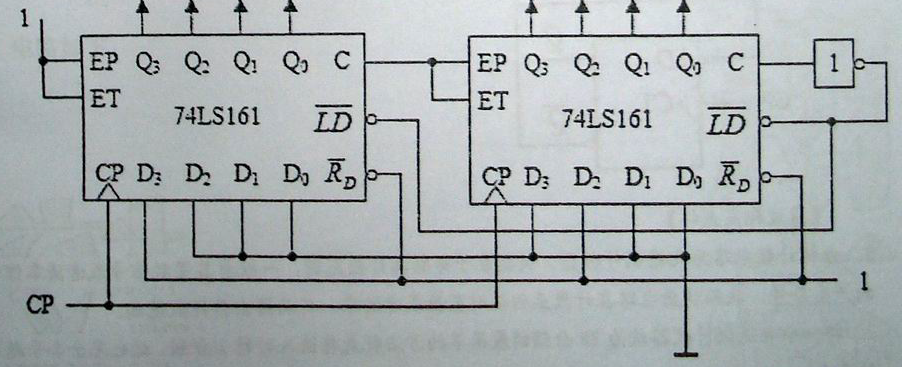

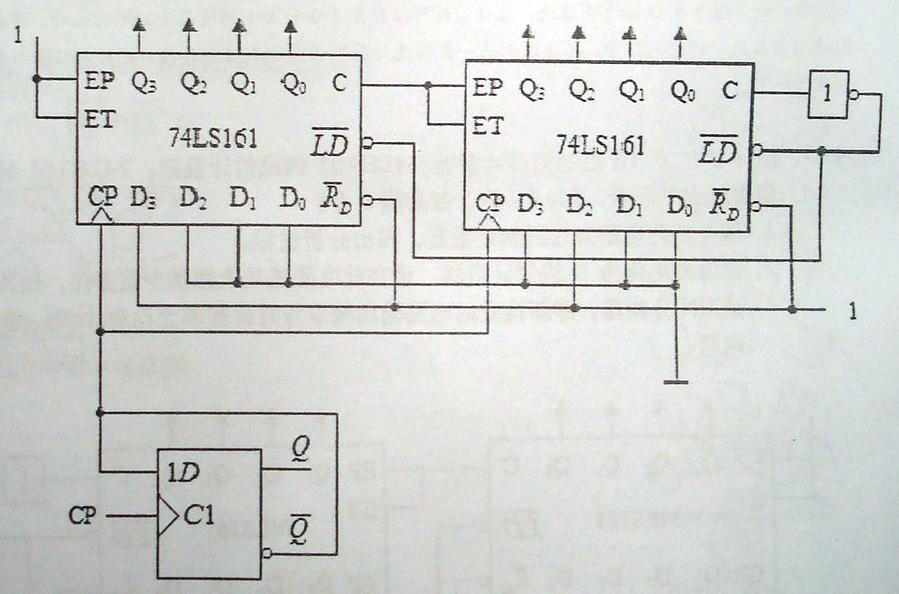

十一、给出二片16进制同步计数器构成的计数器:

(1)分析电路是几进制计数器;

(2)假设时$N$进制计数器,在电路基础上添加器件使其变为$2N$分频器(就是变成$2N$进制)。

思路:

(1)当计数器计数至$11111111$时$C$产生进位脉冲,同时将计数器置数为$01001000$;故计数范围是$01001000\sim 11111111(72\sim 255)$,故是$255-72+1=184$计数器。

(2)只要将输入时钟二分频即可。(利用$D$触发器,$CP$作为$D$触发器的时钟,将输出$\overline Q$连接在$D$上即可实现二分频)

08年真题

十、用两块十进制同步加法计数器74LS160及必要的其它器件实现可变模计数器。当$A=0$,实现$36$进制计数器;当$A=1$,实现$100$进制计数器,且不能有过渡状态。

解:因为不能有过渡态,所以我们采用置数的方式返回(清零是异步的,中间会有过渡)。

- 当$A=0$时,$36$进制,计数循环是$0000\ 0000\sim 0011\ 0101$;

- 当$A=1$时,$100$进制,计数循环是$0000\ 0000\sim 1001 \ 1001$;(答案里说要在$1001 \ 1001$时给一个置数信号,但我觉得如果是两块同步加法计数器实现的话,默认不就是$100$进制吗,这里按答案来)。

故$\overline {LD}=\overline {\overline AQ_2Q_0Q_5Q_4+AQ_3Q_0Q_7Q_4}$,进位:$Y=\overline{\overline {LD}}$,预置数为全$0$。

故电路图为: