用触发器设计计数器

用JK触发器设计计数器

04年真题

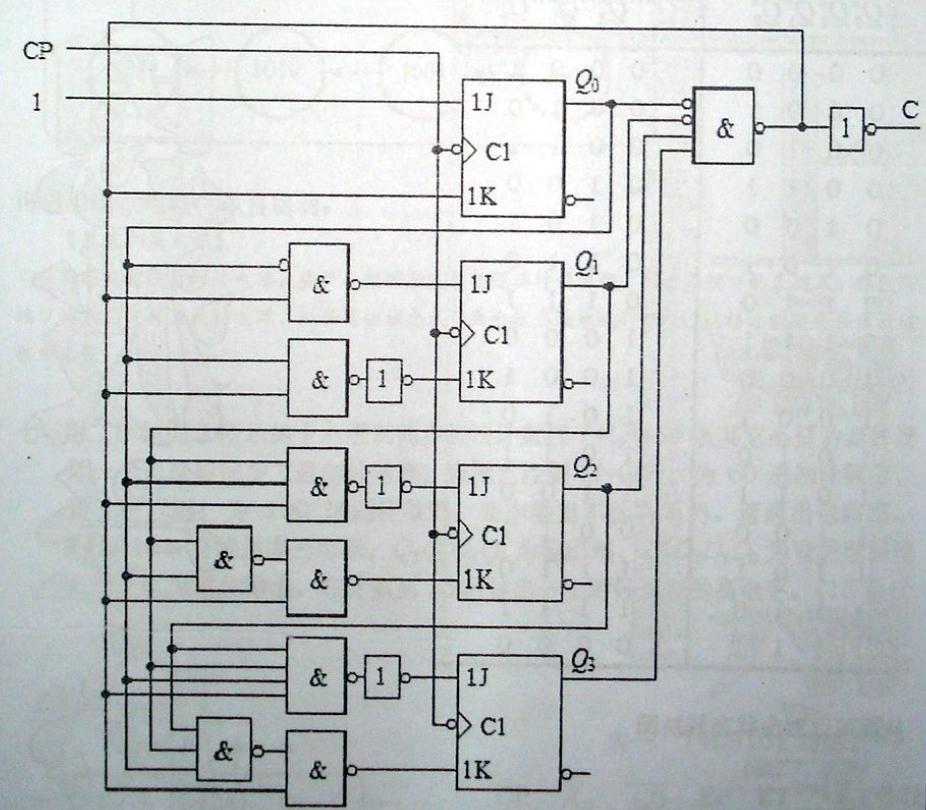

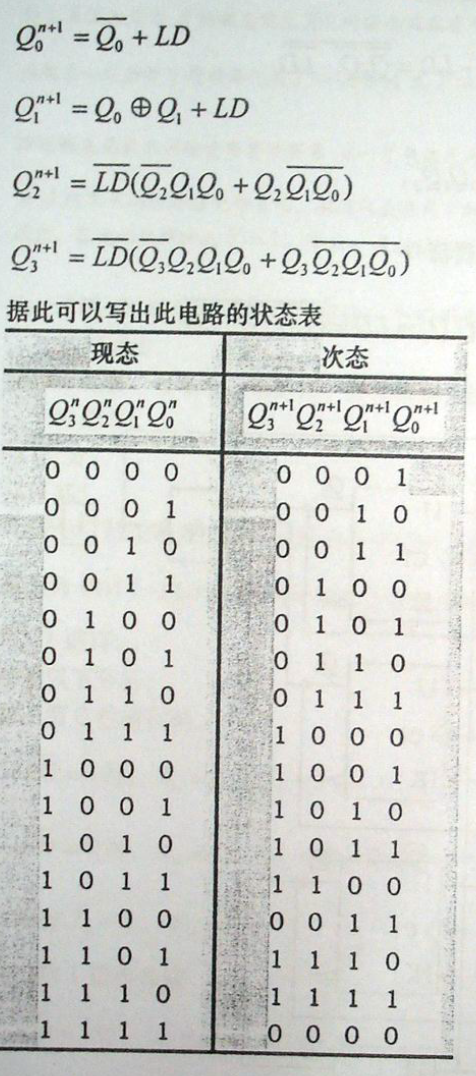

六、用JK触发器及与非门设计一个采用余3码的能置初态于十进制0状态的十进制加法计数器。画出电路图、状态图,说明电路能否自启动。

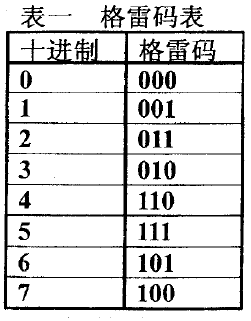

思路,余3码的0~9是0011~1100,故当计数器计数至$1100$时产生置数信号$\overline {LD}$,给其置数0011即可。分析:

- 对于第0位寄存器,$\overline {LD}=1$时,$J=1,K=1$;$\overline {LD}=0$时,$J=1,K=0$,寄存器置1。

- 对于第1位寄存器,$\overline {LD}=1$时,$J=Q_0,K=Q_0$;$\overline {LD}=0$时,$J=1,K=0$,寄存器置1。

- 对于第2位寄存器,$\overline {LD}=1$时,$J=Q_1Q_0,K=Q_1Q_0$;$\overline {LD}=0$时,$J=0,K=1$,寄存器置0。

- 对于第3位寄存器,$\overline {LD}=1$时,$J=Q_2Q_1Q_0,K=Q_2Q_1Q_0$;$\overline {LD}=0$时,$J=0,K=1$,寄存器置0。

故有:

电路为:

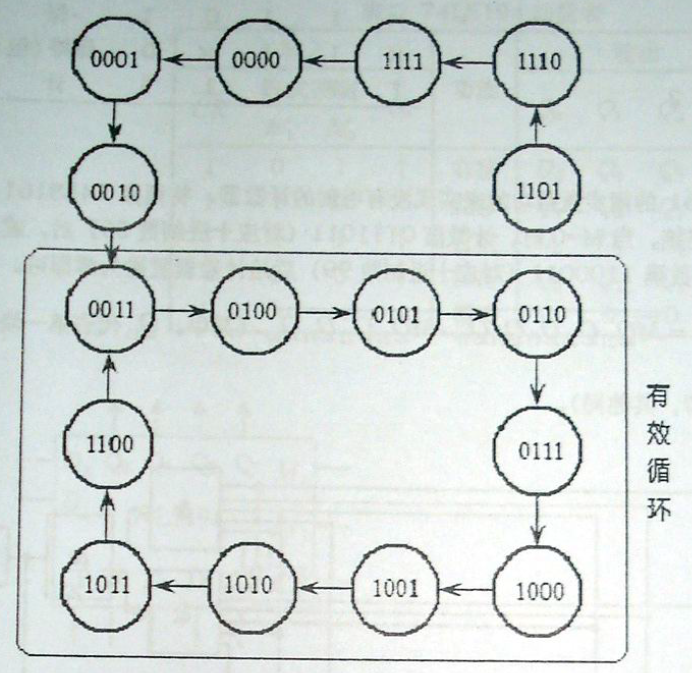

由JK触发器的逻辑特性方程:$Q^{n+1}=J\overline {Q^n}+\overline KQ^n$,可状态方程,并得到状态表:

从而可以画出状态转移图:

08年真题

八,用主从JK触发器和门电路设计一个可控同步加法计数器,当$M=0$,实现采用自然二进制码的六进制计数器,当$M=1$时,实现三位格雷码的八进制计数器,且都具有进位输出$Y$。

思路:写出状态表→根据卡诺图化简,写出状态方程和输出方程→写出激励方程→画电路图

解:

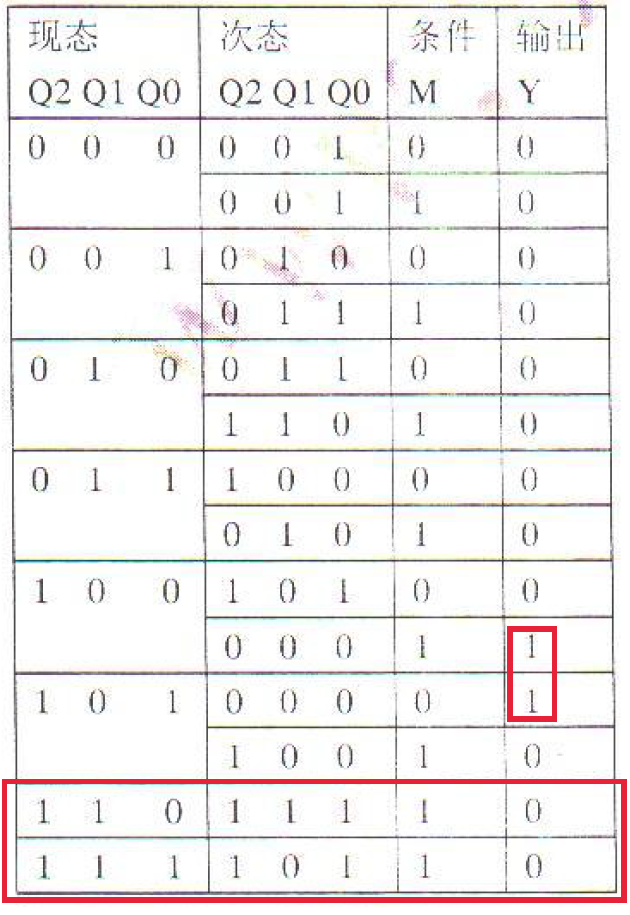

①. 写出状态表(图中红框区域表示应该注意的地方:1. 注意输出$Y=1$对应的现态;2. 注意三位格雷码还有两个现态110和111)

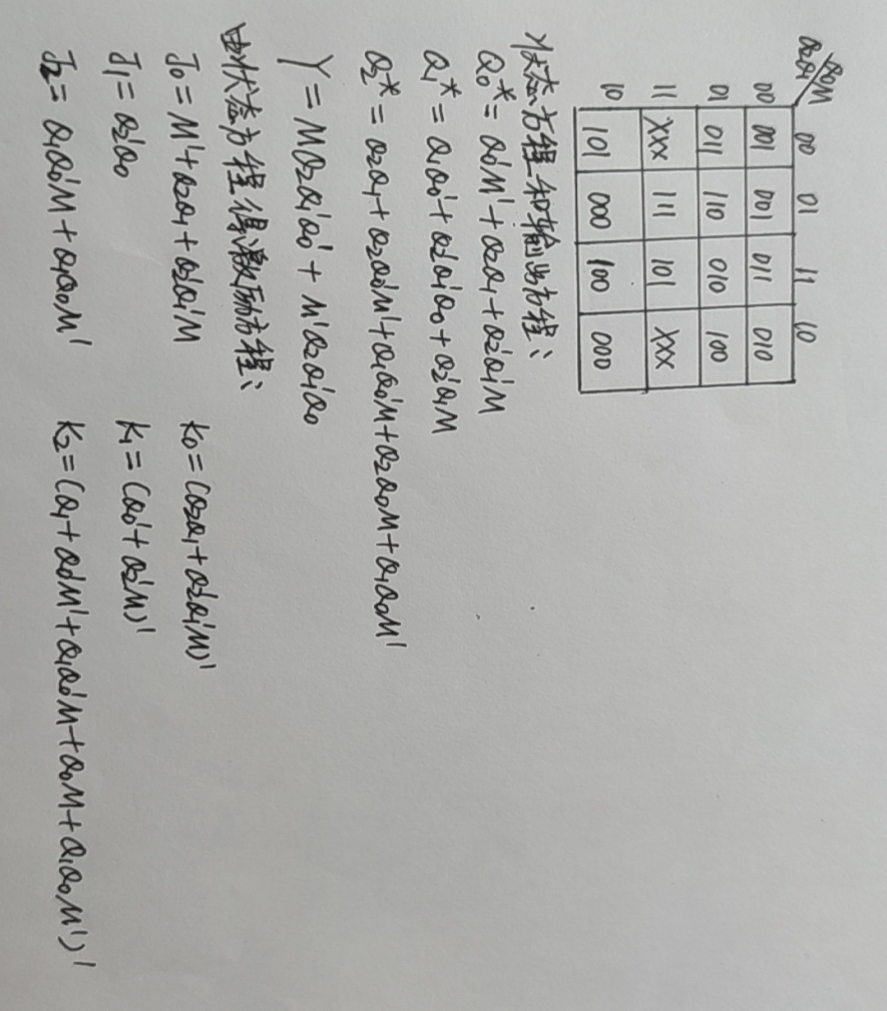

②. 画卡诺图,写状态方程和输出方程,并由状态方程写出激励方程

③. 画出电路图,省略。(太复杂了,两份答案里都给省略了。。)

09年真题

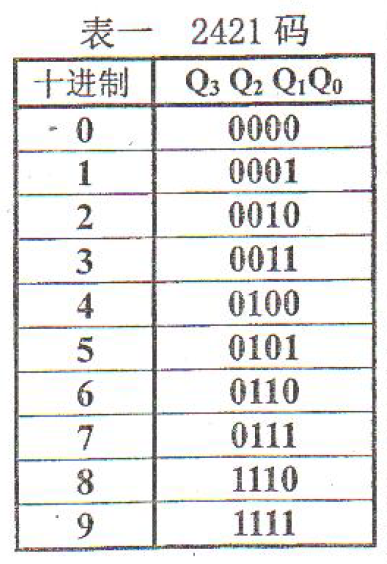

八、用JK触发器及门电路设计一个同步十进制加法计数器(2421码),电路在9到0时有进位输出Y。检查设计的电路能否自启动。

①. 列出状态转移表。

②. 根据状态转移表分别画出$Q_3,Q_2,Q_1,Q_0$的卡诺图,并得到状态方程和输出方程,再由输出方程写出激励方程。

③. 画出电路图(略)。

④. 列出状态转换图,判断电路能否自启动。

用T触发器设计计数器

11年真题

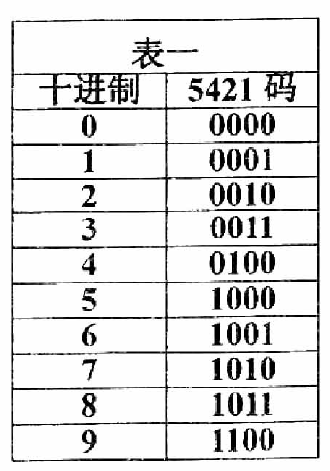

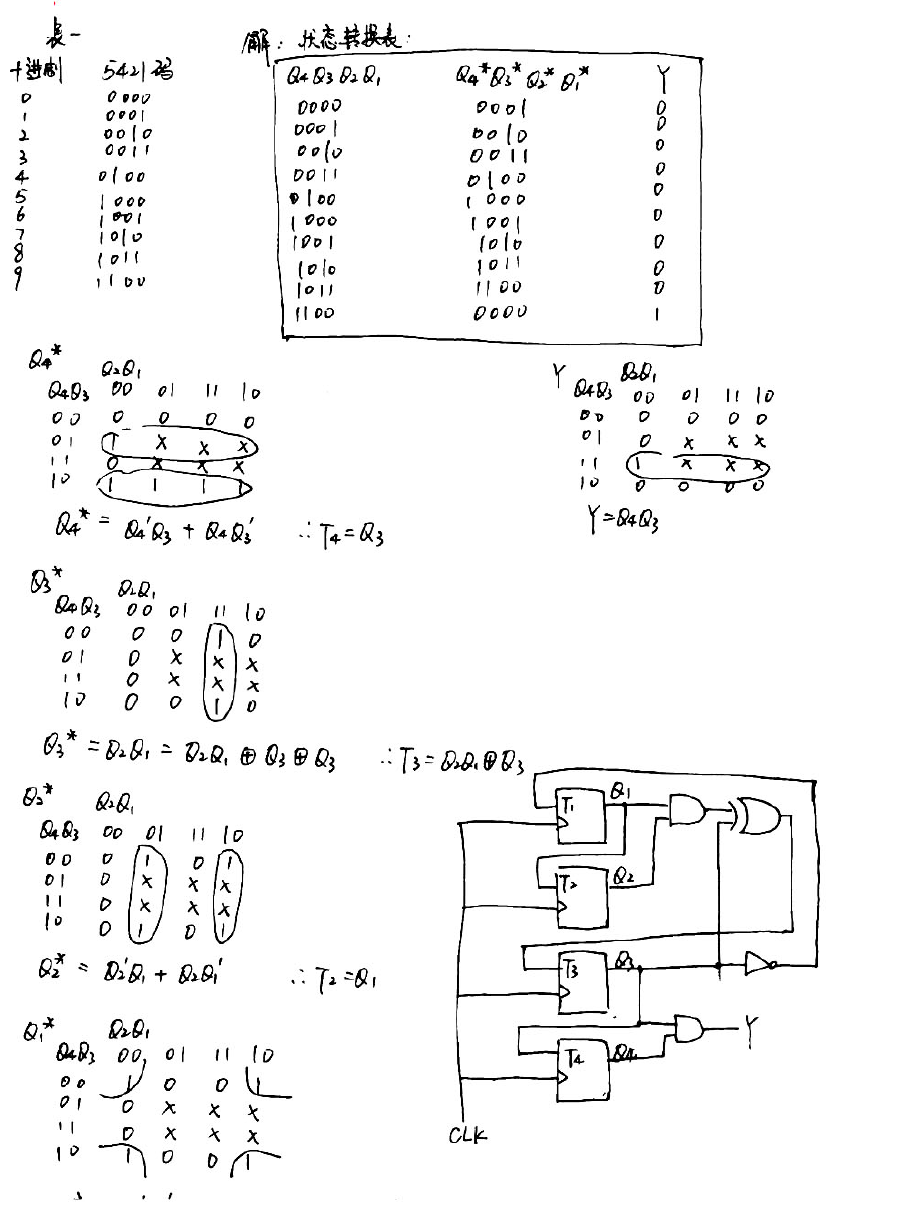

七、用下跳变触发的T触发器及门电路设计一个采用5421码的同步十进制加法计数器,计数器在9到0时有进位输出Y。写出设计过程、驱动方程、激励方程、输出方程、画出逻辑电路图,不用检查自启动。

思路:写出状态表→画卡诺图→写方程(状态、激励、输出)→画电路图

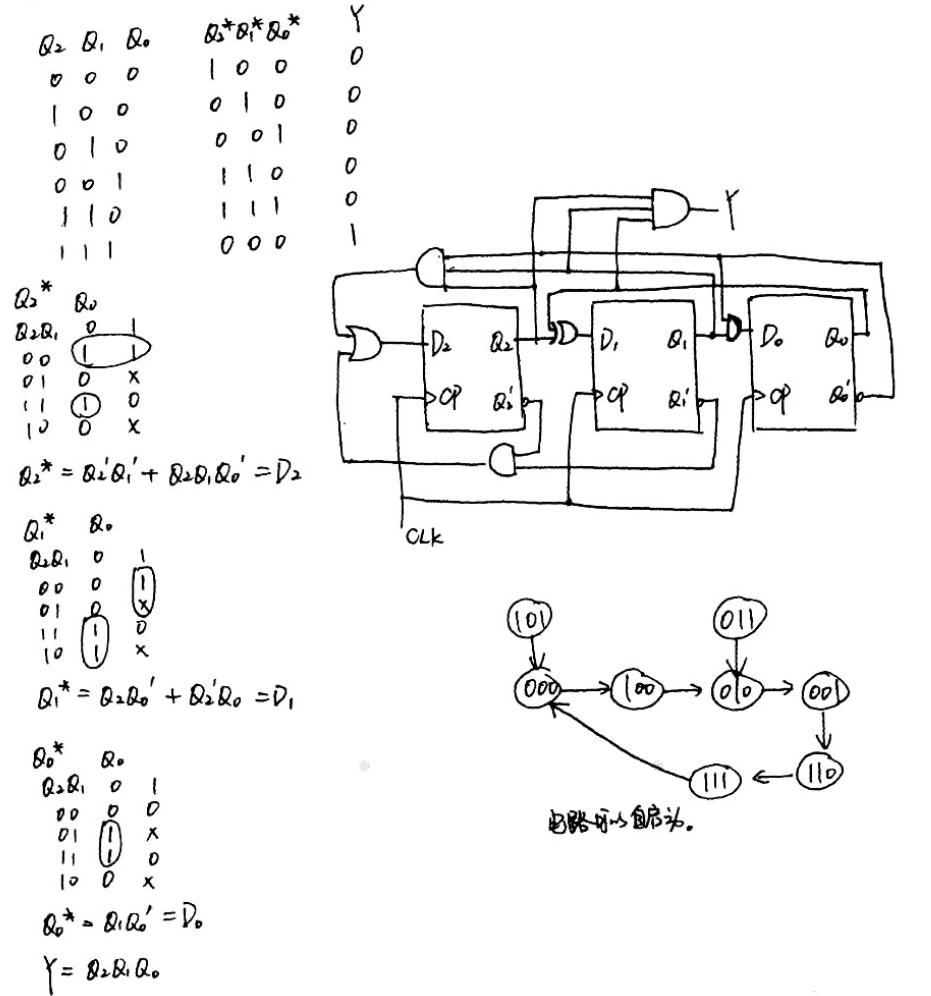

用D触发器设计计数器

12年真题

八、用D触发器及门电路设计6进制同步加法计数器,0到5的计数编码分别为000,100,001,110,111。计数器在计数5到0时有进位输出Y。写出设计方程、驱动(激励)方程、输出方程,画出逻辑电路图,并画出完整状态图,判断能否自启动。

思路:写状态表→画卡诺图,得到状态、输出、激励方程→画电路图→画状态图