微机原理 第二章:微处理器及其体系结构

2.1 微处理器的主要性能指标

字长

计算机一次所能处理的数据的位数(8位机、16位机)

- 字长决定了PC机的运算能力和运算精度;

- 字长由CPU数据总线的条数决定;

- 字长决定了通用寄存器、运算器和内部缓冲器的位数。

运算速度

- 基本指令的执行时间;

- CPU主频的大小决定的运算速度的大小。

访存空间

- 微处理器所能访问的存储单元数(存储容量);

- 存储单元数由地址总线条数决定。

2.2 8086微处理器

2.2.1 8086内部结构

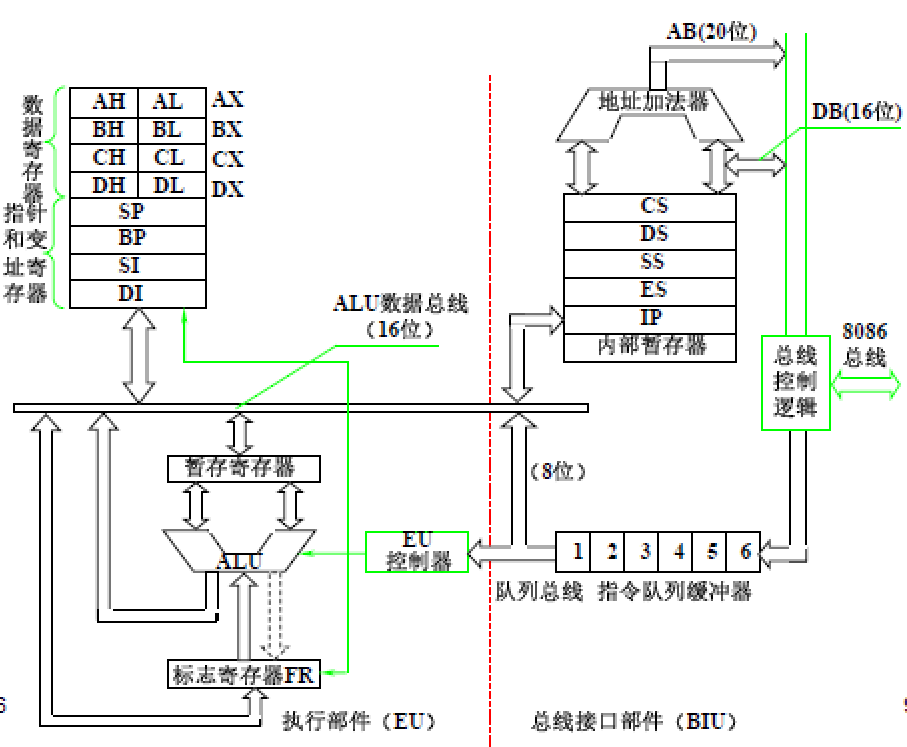

8086CPU内部从功能上看有两个独立的工作部件:

这样可以使取指令和执行指令同时进行,提高运算速度。

①. 执行部件EU(Execution Unit):

作用:负责指令的执行,不与外部总线打交道。

②. 总线接口部件BIU(Bus Interface Unit)

作用:和总线打交道,根据EU的请求,执行CPU对存储器或I/O接口的总线操作,完成数据传送。

2.2.2 8086寄存器结构

(13个16位寄存器,1个16位状态标志寄存器)

允许各逻辑段在整个存储空间浮动,段与段之间可以是连续的,也可以是分开的或重叠的

8个通用寄存器

数据寄存器

数据寄存器特有的习惯用法:

AX(Accumulator)

①. 在I/O指令中:

输入指令:

长格式:IN AX,PORT;短格式:IN AX,DX

输出指令:

长格式:OUT PORT,AX;短格式:OUT DX,AX

②. 在乘法类指令MUL和IMUL中:

MUL BL ;AL中和BL中的8位数相乘,乘积放在AX中

IMUL BX ;AX与BX中的16位带符号数相乘,结果放在DX和AX中

③. 在除法指令中,除数为8位时,被除数固定放在AX中;除数为16位时,被除数的低位固定放在AX中(高位DX),商放在AX中;

DIV CL ;被除数放在AX中

IDIV CX ;被除数放在DX、AX中

AH

①. 在DOS功能调用中,将功能号置给AH

MOV AH,4CH

INT 21H ;返回DOS

②. 在除法指令中,除数是8位时,运算得到的余数在AH中

DIV CL ;实现(AX)/(CL),所得商在AL中,余数在AH中

AL

①. 在I/O指令中:

输入指令:

长格式:IN AL,PORT;短格式:IN AL,DX

输出指令:

长格式:OUT PORT,AL;短格式:OUT DX,AL

②. 在加法调整指令DAA和AAA中,加数的和必须放在AL中才能进行调整;

③. 在乘法指令中,如果是两个8位数相乘,一个操作数隐含在固定的AL中;

MUL BL ;AL中和BL中的8位数相乘,乘积放在AX中

④. 在除法指令中,除数是8位时,运算得到的商在AL中

DIV CL ;实现(AX)/(CL),所得商在AL中,余数在AH中

⑤. DOS功能键盘输入一个字符,送入的字符放在AL中

串搜索指令、存字符串指令、取字符串指令都是默认的要处理的数据所在位置为AL(AX)。

BX(Base)

①. 进行存储器时,作为基址寄存器。

CX(Count)

①. 串操作时,存放重复前缀的循环次数

MOV CX,100

REP MOVS AREA2,AREA1 ;重复传送直到(CX)=0为止

②. 在循环控制指令中,必须以CX作为计数器

LOOP GOON

相当于:

DEC CX

JNZ GOON

CL

①. 在移位和循环移位指令中,存放执行一次指令移动的位数n:

SAL AX,CL ;将AX中的内容左移n位,n是CL中的内容

ROR BYTE PTR[DI],CL ;(CL)=8,则(DI)所指内存的内容不含进位右移8位

DX(Data)

①. 在使用短格式I/O指令时,应先将端口地址赋给DX:

MOV DX,02F0H

IN AX,DX ;端口输入

MOV DX,02F1H

OUT DX,AX ;端口输出

②. 在乘法指令中,若是字相乘,则结果的高位放在DX中;

MUL BX ;AX与BX中的16位带符号数相乘,结果放在DX和AX中

③. 在除法指令中,当除数是16位时,被除数的高位放在DX中(低位AX),余数放在DX中;

DIV CX ;被除数放在DX、AX中

④. 在DOS功能中,字符串输入或输出时,字符串的首地址均存放在DS:DX中

DL

①. DOS功能中,输出字符的ASCII码要先存入DL中

MOV AH,02H

MOV DL,'X'

INT 21H

指针寄存器

SP(Stack Pointer):堆栈指针寄存器,存放栈顶的偏移地址;

BP(Base Pointer):基址指针寄存器,用于在访问内存时存放内存单元的偏移地址。

变址寄存器

SI(Source Index):源变址寄存器,存放源操作数的偏移地址;

DI(Destination Index):目标变址寄存器,存放目标操作数的偏移地址。

4个段寄存器

用于存放逻辑段的段基地址。

指令指针寄存器IP

16位

其内容为下一条要执行的指令的偏移地址,引导程序顺序执行。

程序员不能直接读写!!!

状态标志寄存器F

6个状态标志位:

①. 进位标志CF(Carry Flag):若CF=1,则表示结果的最高位上产生了一个进位或借位;

②. 辅助进位标志AF(Auxiliary Carry Flag):辅助位表示低4位有无进位或借位;

③. 奇偶标志PF(Parity Flag):PF=1 运算结果1的个数为偶数;PF=0 运算结果1的个数为奇数;

④. 溢出标志OF(Overflow Flag):对带符号数的算数运算是否产生了算术溢出;用$OF=Cs\bigoplus Cp=$(最高位是否有进位$\bigoplus$次高位是否有进位)来检验是否有溢出;

⑤. 零标志位ZF(Zero Flag):ZF=1 运算结果为0;ZF=0 运算结果不为0;

⑥. 符号标志位SF(Sign Flag):SF=1 负;SF=0 正。

CF可用来表示无符号位的溢出;OF用来表示有符号位的溢出。

3个控制标志位:

①. 方向标志DF(Direction Flag):控制数据串操作指令的步进方向。DF=1 减址方;DF=0 增址方式;

②. 中断允许标志IF(Interrupt Enable Flag):对可屏蔽中断:IF=1 开中断;IF=0 关中断;

③. 陷阱标志TF(Trap Flag):TF=1 单步执行,以检查程序;TF=0 连续正常执行。

2.2.3 8086的存储器组织

8086CPU的内存地址空间为 1MB

8086的存储格式

实际地址和逻辑地址

逻辑地址:产生实际地址用到的两个地址(段首址:偏移地址)

实际地址:CPU和存储器进行数据交换时使用的地址

实际地址唯一,逻辑地址不唯一;一个实际地址可以对应多个逻辑地址。

堆栈

堆栈:在内存中开辟的暂时存放数值数据和地址数据的一段存储区(堆栈段),“先进后出“,16bit~64KB

8086堆栈操作:入栈PUSH和出栈POP,均为16字操作,在栈顶进行。

在堆栈中存取数据的地址由SS和SP规定:SS存放堆栈段首址,SP存放栈顶的偏移地址。

压栈是先压高字节,后压低字节。

2.2.5 8086时钟周期和总线周期

时钟周期:CPU的基本定时单位,由主频决定,是CPU的时间基准;

总线周期:CPU读或写一次存储器或I/O端口所需的时间;8086一个最基本的总线周期由4个时钟周期组成。

一个最基本的读或写周期包含4个T状态,有可能在T3和T4中间插入一个或几个等待状态Tw。

2.2.7 I/O端口组织

端口号(端口地址):为每个I/O端口分配的地址,具有唯一性。

微机I/O端口有两种编址方式:

①. 统一编址(存储器映像编址的I/O)

I/O端口地址置于存储器空间中,和存储单元统一编址。

②. 独立编址

I/O和存储器使用同一地址,使用指令M/IO加以区分,地址利用率高,8086即为此种端口编址方式。

凡是设有专门输入指令IN和输出指令OUT的CPU对I/O端口都进行独立编址。

独立编址采用20条地址总线中的16条(A0-15)地址线对端口地址进行编址,端口地址不分段,所以不需要采用段寄存器。

8086端口地址仍为20位,高四位为0