数电特殊题型总结

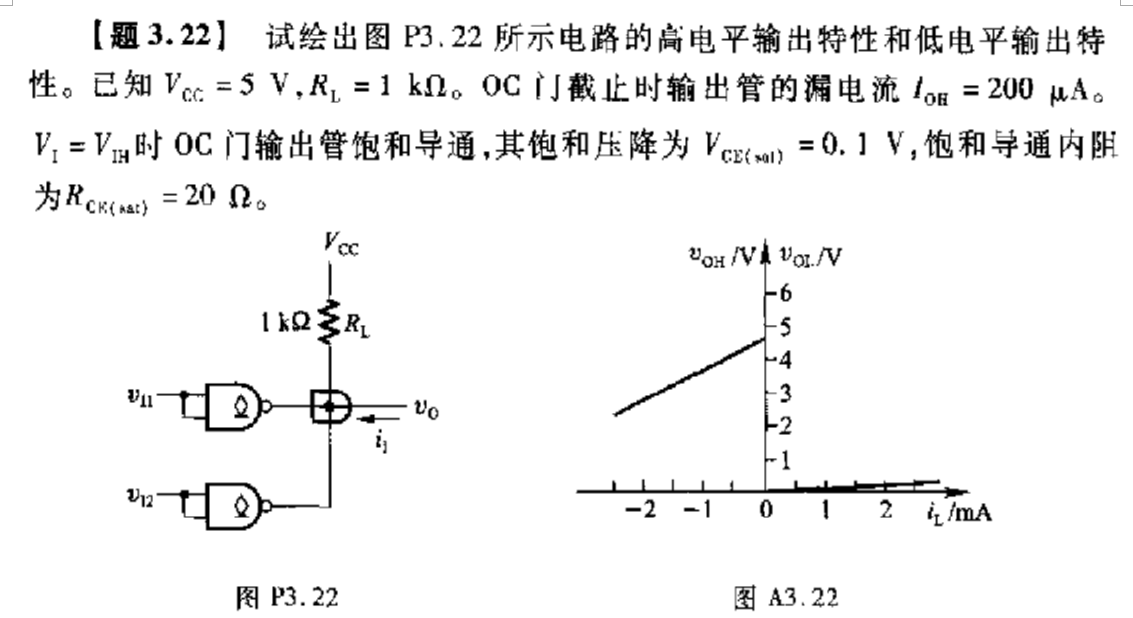

第三章 门电路

一、双极型三极管工作状态的计算

为使三极管开关电路中的三极管工作在开关状态,须保证输入低时三极管截止,输入高时三极管饱和导通。

因此,这类题要求计算输入为高、低时三极管的工作状态,来判断电路参数选择是否合理。

解题步骤:

①. 利用戴维南定理将输入电路简化为等效的$V_E,R_E$串联电路,如下图:

②. 计算$v_i$为低电平时的$V_E$,若$V_E<V_{ON}$,则认为三极管截止,设计合理;否则三极管导通,设计不合理。

③. 计算$v_i$为高电平时的$V_E$以及此时的$i_B$,并与临界饱和基极电流$I_{BS}$比较。若$i_B>I_{BS}$,则三极管饱和导通,参数设计合理;否则不饱和导通,设计不合理。

相关题目:指导书例3-1,课本课后题3-11,3-12(增加了输入悬空的情况)

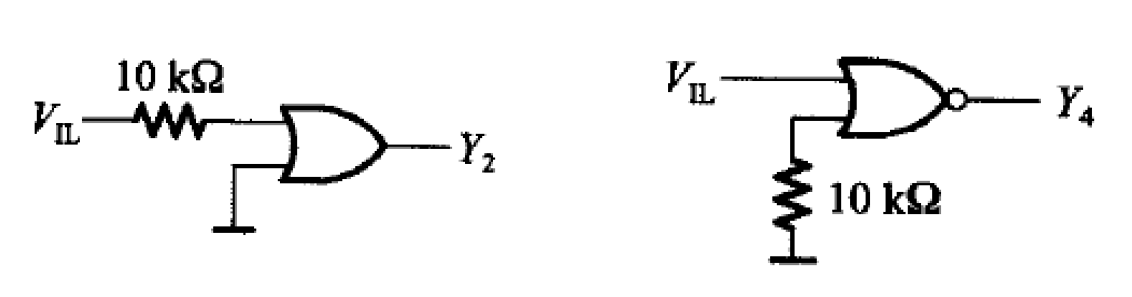

二、集成门电路逻辑功能的分析

两种情况:

①. 给出门电路输入的电压波形或逻辑状态,求输出的电压波形或逻辑状态。

解题方法:

对CMOS门电路而言,通常不允许输入端工作在悬空状态;输入端经电阻接地时,与接逻辑低电平等效;经过电阻接电源电压时,与接逻辑高电平有效。

对TTL门电路而言:

- 输入端的悬空状态和接逻辑高电平等效。

- 输入端经过电阻(通常几十千欧以内)接电源电压时,与接逻辑高电平有效。

- 输入端经过电阻接地时,输入端的电平与电阻阻值的大小有关,

- 当阻值很小时(例如只有几十欧姆),输入端相当于接低电平;

- 当电阻阻值大到一定程度后,输入端电压将升高到逻辑高电平。例如74系列门电路中,当这个电阻大于2kΩ,输入端电压将高于1.4V,这时输入端状态与接逻辑高电平等效。

例如下图左电路输出的是高电平,右电路输出的是低电平。

相关题目:电压波形:课本课后题3-2、3-4、3-8;课本课后题3-14、3-15

②. 给出了集成门电路的内部电路结构图,求它的逻辑功能。

解题方法:

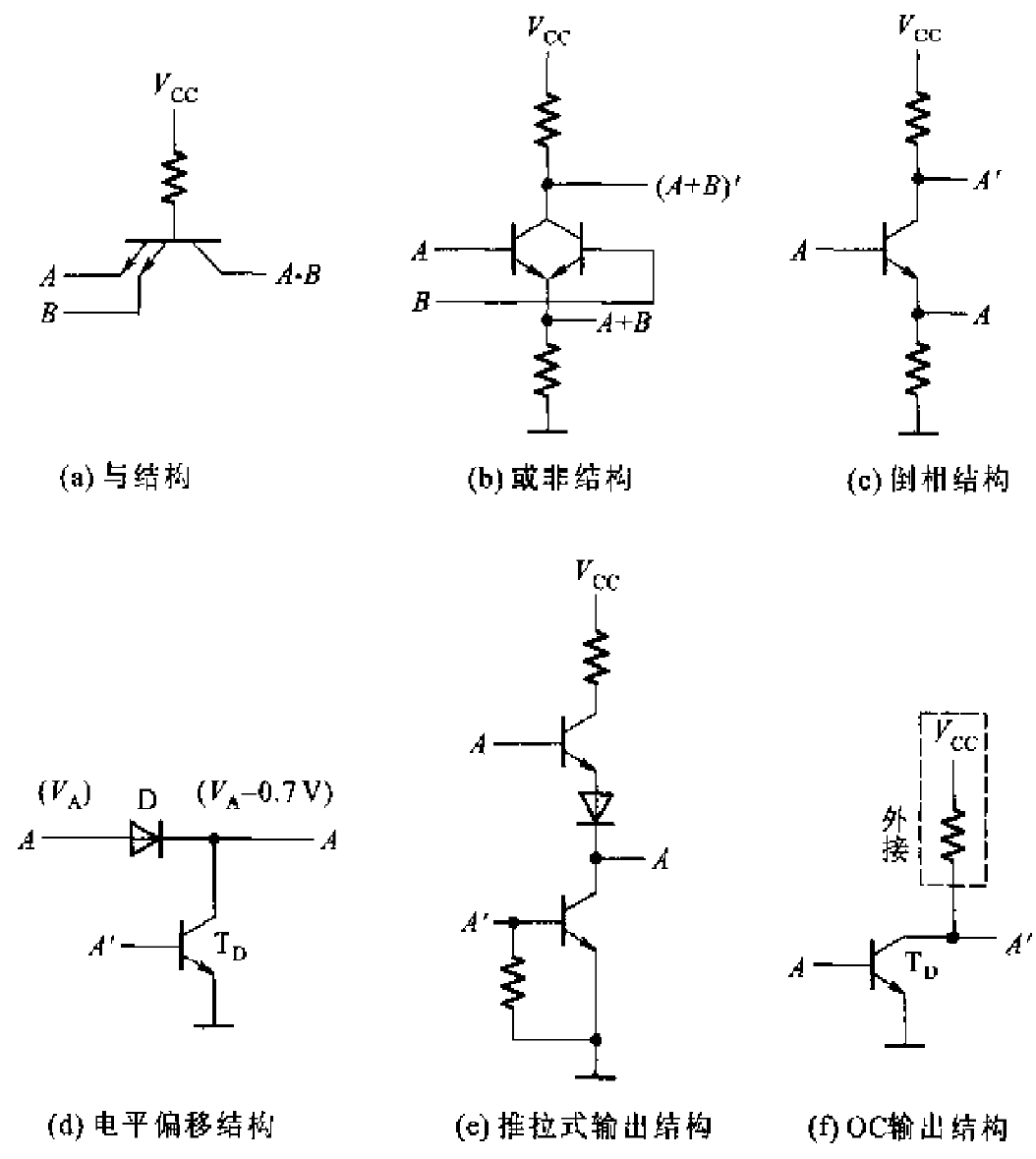

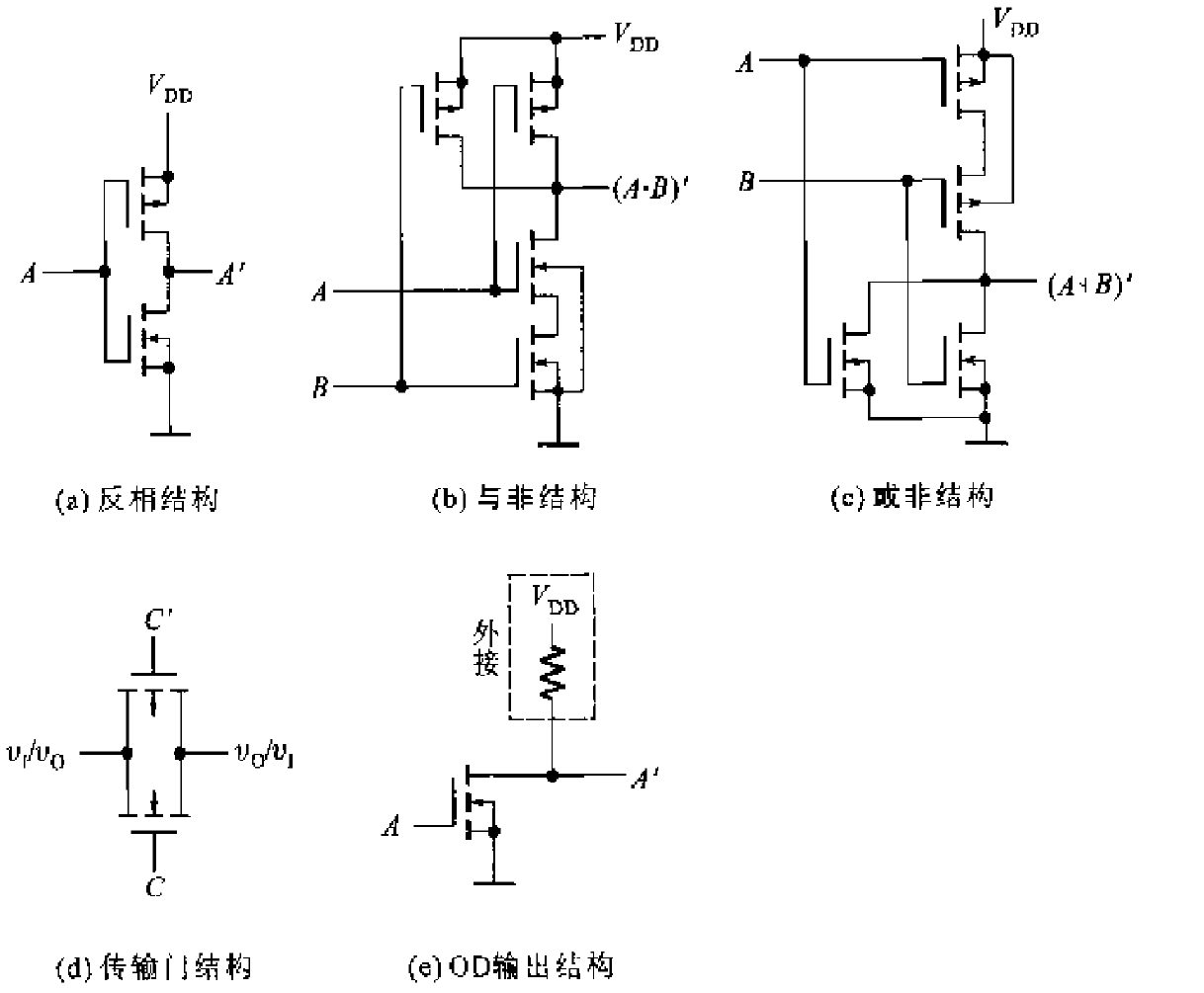

- 首先将电路划分为若干个基本结构模块,

- 从输入到输出一次写出每个模块的逻辑关系式,最后就得到了最终的逻辑表达式。

相关题目:指导书例3-2、例3-3,课本课后题3-7、3-13

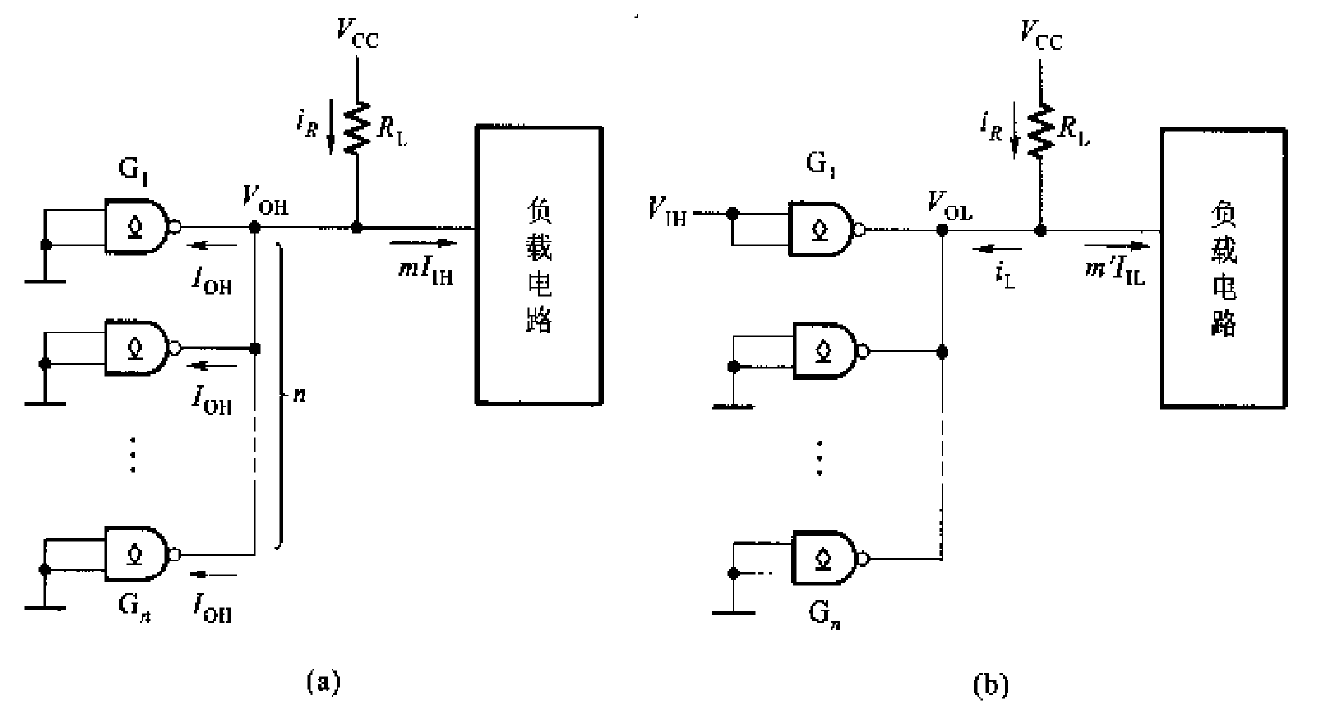

三、TTL电路扇出系数的计算(21年考了)

扇出系数:指一个门电路可以同时驱动某一种门电路的最大数目。

解题方法:

题干一般会给出四个参数:

- 驱动门的低电平输出电流最大值$I_{OL(max)}$,和高电平输出电流最大值$I_{OH(max)}$

- 负载门的低电平输入电流最大值$I_{IL(max)}$,和高电平输出电流最大值$I_{IH(max)}$

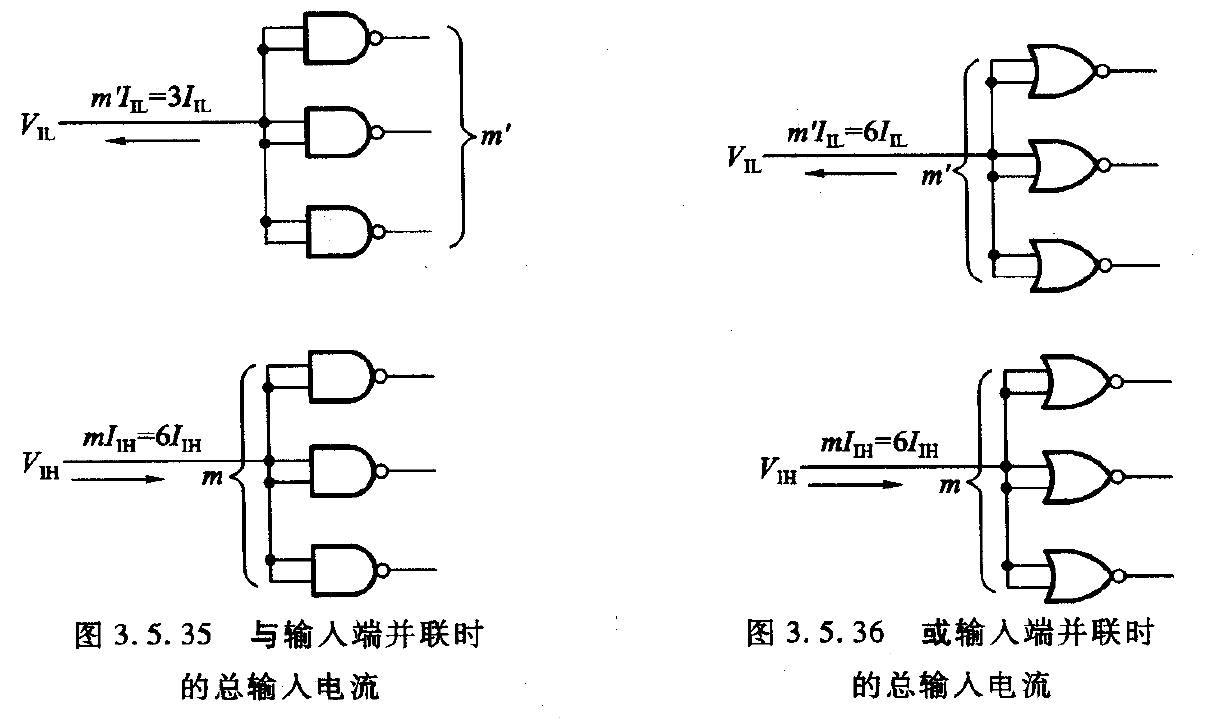

计算在$I_{OL}\le I_{OL(max)}$的条件下,驱动门能驱动负载门的数目$N_1$:

负载为或/或非门时,$k$等于每个门的并联输入端个数;负载为与/与非门时,$k=1$。

- 计算在$I_{OH}\le I_{OH(max)}$的条件下,驱动门能驱动负载门的数目$N_2$:

$p$是每个负载门的并联输入端个数。

相关题目:指导书例3-4,课本课后题3-16、3-17

四、TTL电路输入端串联电阻允许值的计算

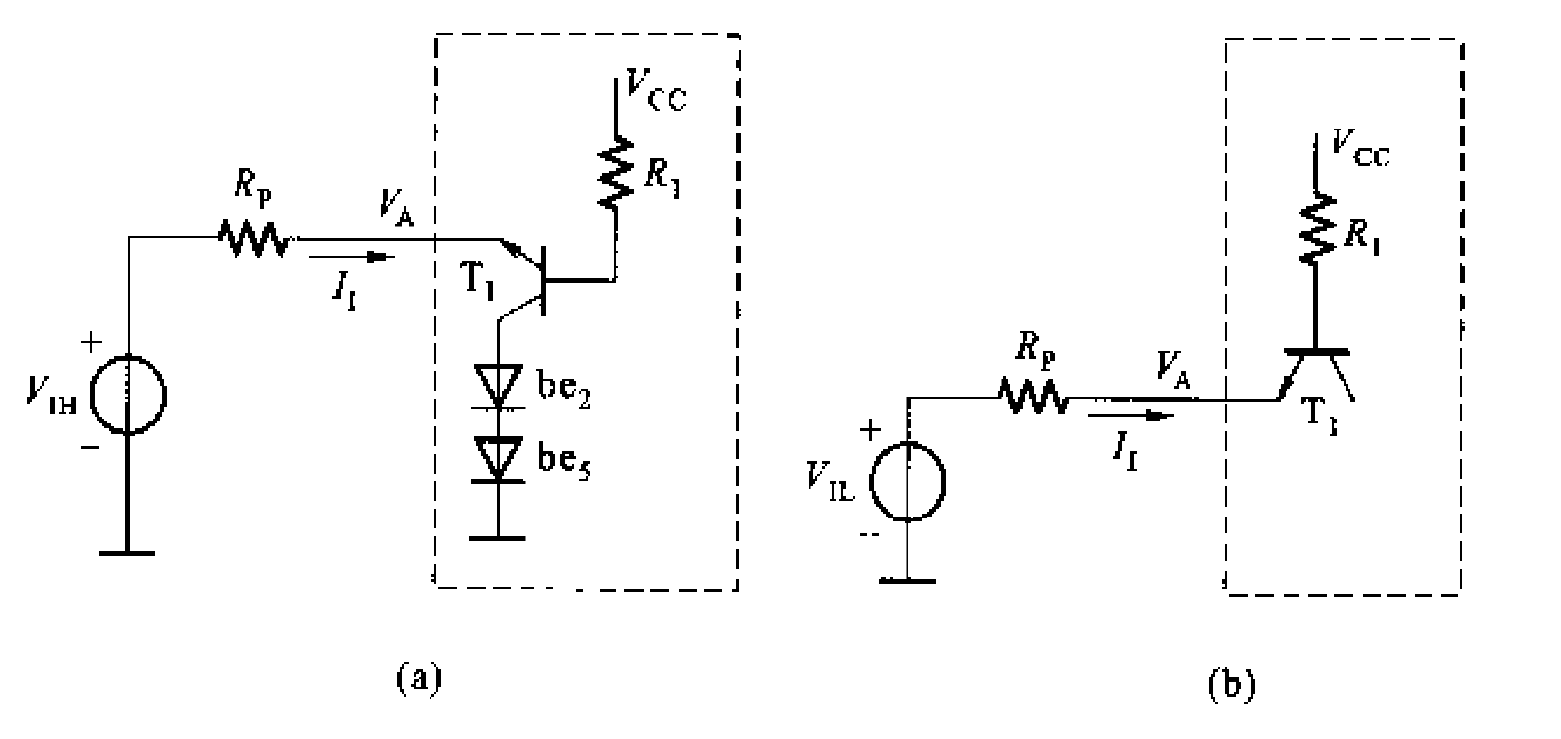

- 当输入为高电平时,由图(a),若$R_P$过大,则加到门电路输入端的$V_A$将低于规定的$V_{IH(min)}$,是不允许的

- 当输入为低电平时,由图(b),若$R_P$过大,则$V_A$将高于规定的$V_{IL(max)}$,也是不允许的

解题方法:

- 计算$V_I=V_{IH}$时$R_P$的最大允许值,为保证$V_A\ge V_{IH(max)}$:

- 计算$V_I=V_{IL}$时$R_P$的最大允许值,为保证$V_A\le V_{IL(max)}$

如果$V_A$处有$n$个TTL门电路并联,则可用$R_1/n$代替$R_1$。

相关题目:指导书例3-5,课本课后题3.21

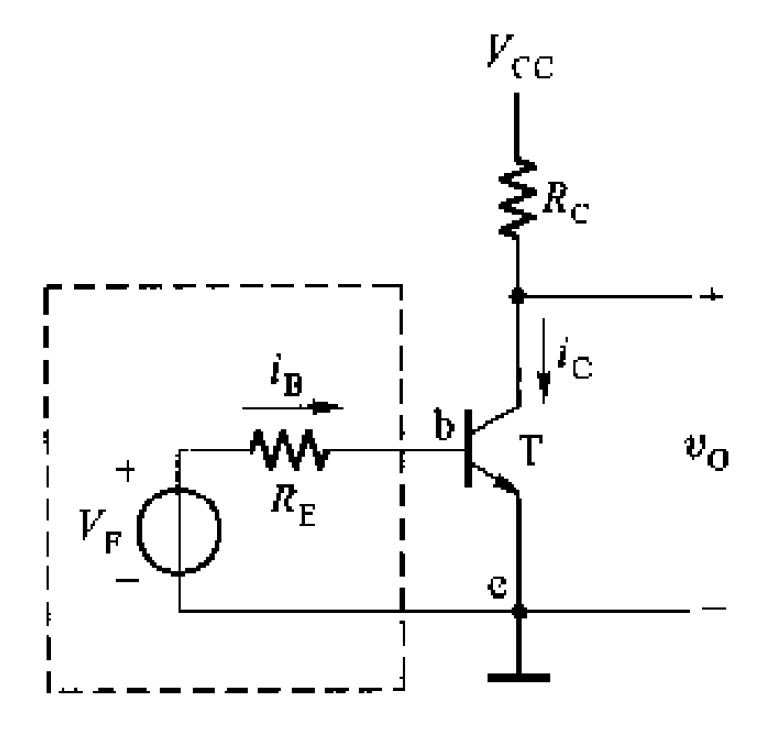

五、三极管接口电路的电路参数计算

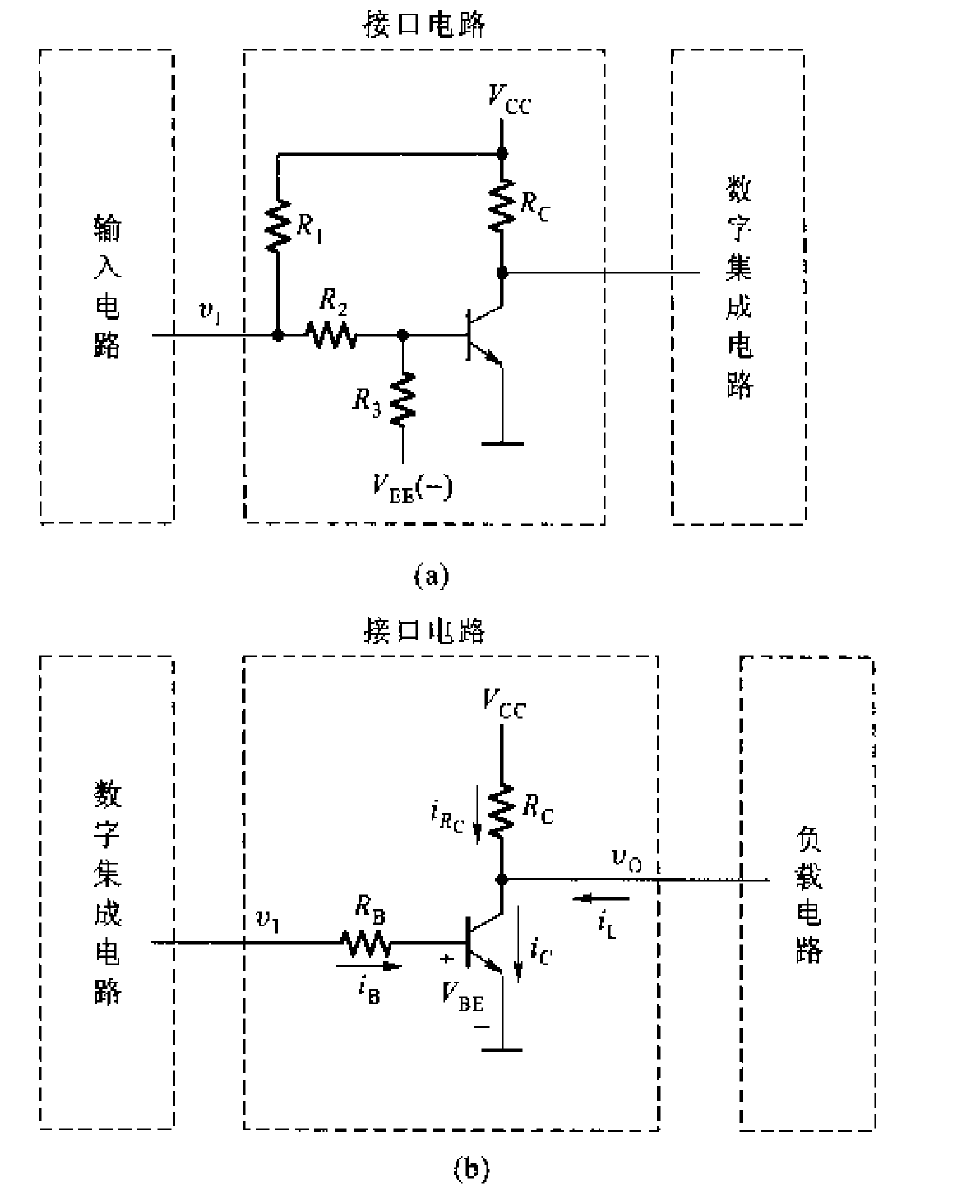

为什么要有接口电路?因为在输入信号的高、低电平与数字集成电路要求的输入电平不同,或者输入信号不能提供数字集成电路所要求的的输入电流时,就需要在输入信号与集成电路之间接入接口电路。

解题方法:

需要保证接口电路在$v_i=V_{OL}$时$v_o$的高电平要高于要求的电压值,在$v_i=V_{OH}$时三极管饱和导通$(v≈0)$。

- 在$v_i=V_{OL}$时,三极管截止,且:

这里的$V_{OH}$是指需要的接口电路输出高电平的最低标准。

- 当$v_i=V_{OH}$时,三极管饱和导通,即:

有时会将$R_{CE(sat)}$和门电路输出电阻$R_O$省略

相关题目:指导书例3-6,课后题3-25、3-26、3-17

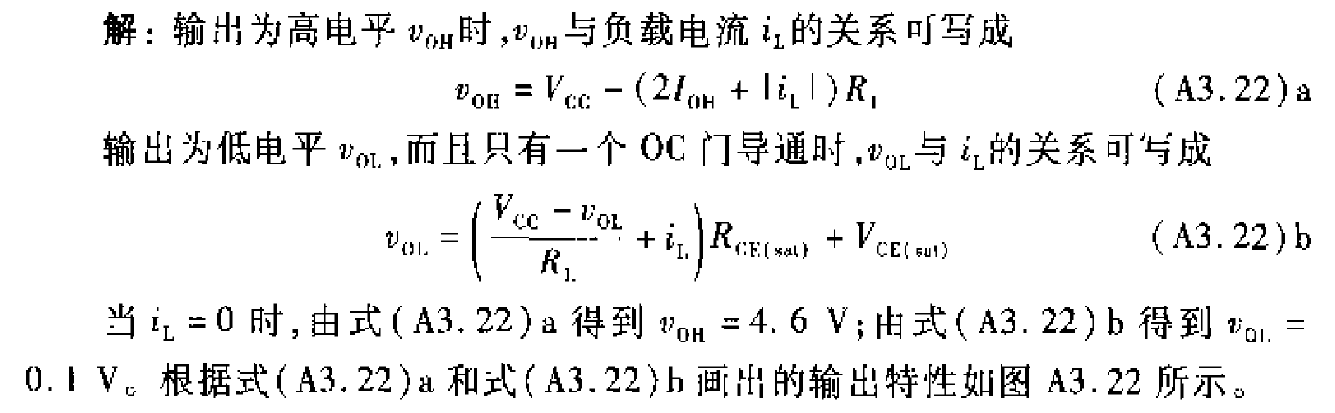

六、OC门和OD门外接上拉电阻阻值的计算

- 当OC门(或OD门)全部截止,输出为高时,为保证$v_o$输出的高电平高于要求的$V_{OH}$值,$R_{L}$不能太大。

其中$m$是负载门电路高电平输入电流的数目。

- 当OC门(或OD门)输出为低,且只有一个OC门导通时,为保证流经$R_L$的电流和负载电路所有的低电平输入电流全部流入一个导通的OC门时,仍然不会超过允许的最大电流$I_{OL(max)}$,$R_L$的阻值不能选的太小。

在负载是CMOS门电路的情况下,$m’=m$,都是负载输入端的个数;

但在负载是TTL门电路时,低电平输入电流的数目不一定与输入端的数目相等:

- 当负载门是TTL或/或非门时,$m’=m$;

- 当负载门是TTL与/与非门时,$m’$等于负载门的个数,而不是输入端的个数。

相关题目:指导书例3-7,课本课后题3-9、3-10(CMOS)、3-23、3-24(TTL)、3-28

七、CMOS门电路静态功耗、动态功耗等参数的计算

相关公式:

静态功耗:$P_S=I_{DD}V_{DD}$,其中$V_{DD}$是电源电压,$I_{DD}$是静态电源电流

动态功耗:$P_D=(C_L+C_{pd})fV_{DD}^2$,其中$C_L$是负载电容,$C_{pd}$是功耗电容,$f$是输入信号频率

总功耗:$P_{TOT}=P_S+P_D$

电源的平均电流:$\overline I_{DD}=P_{TOT}/V_{DD}$

相关题目:课本课后题3-5、3-6

其它