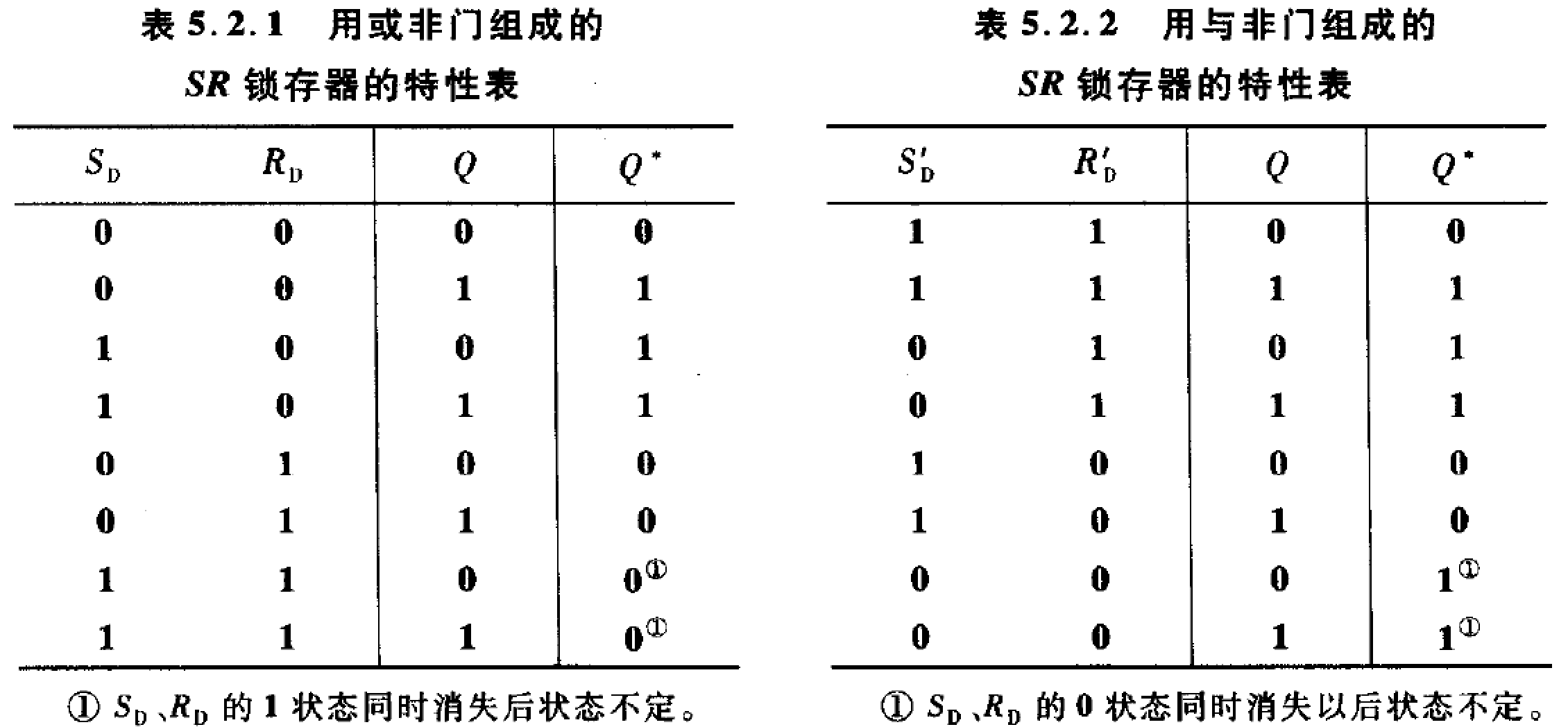

数电 第五章:触发器

考纲:掌握各种触发器(包括基本触发器、电平触发器、一次操作触发器)的状态转换真值表、状态转换方程、激励方程、状态转换图、电路符号;掌握触发器的动态特性;掌握各种触发器的应用及相互变换。

触发器:能够存储1位二值信号的基本单元电路。

触发方式:电平触发、脉冲触发、边沿触发

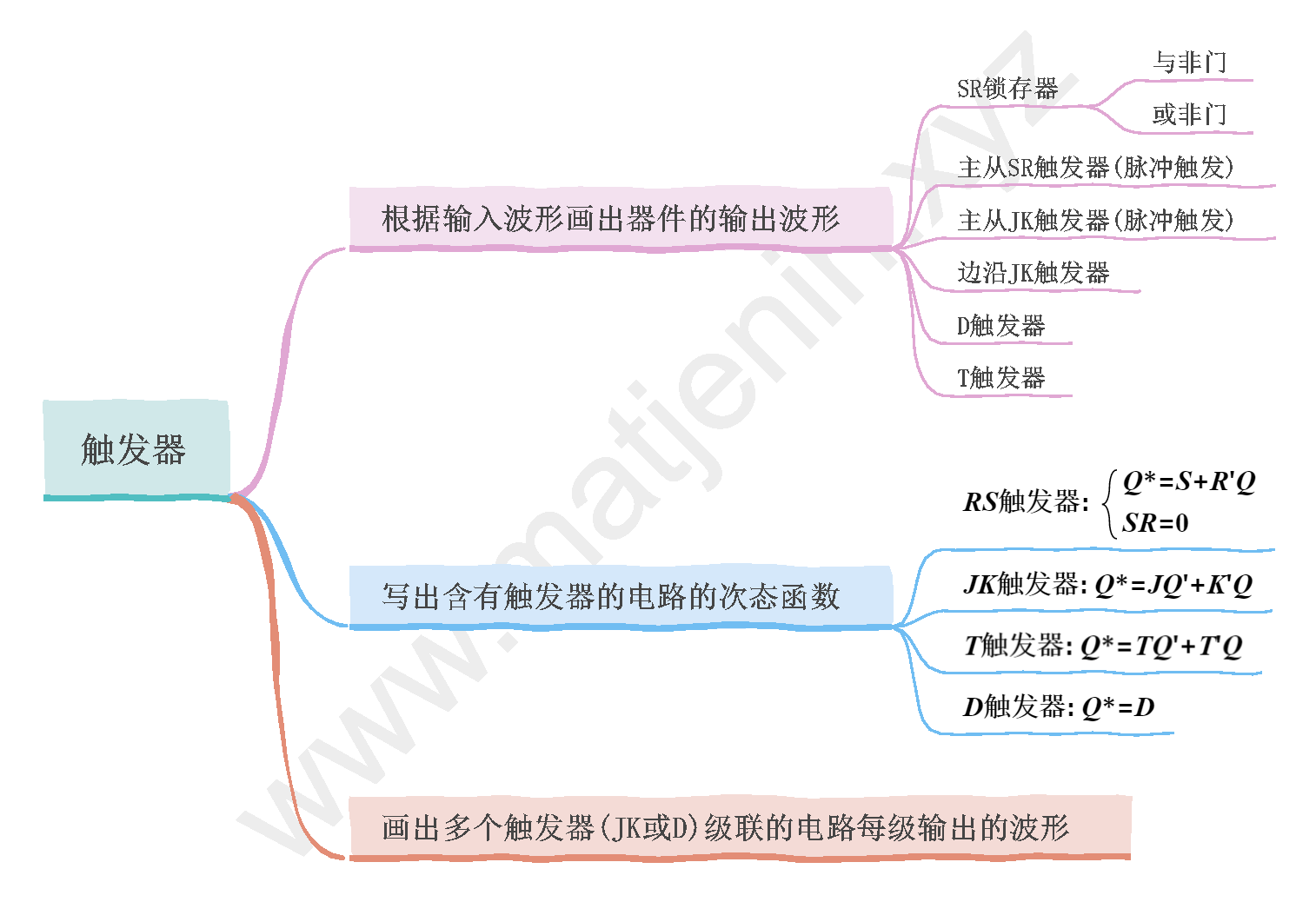

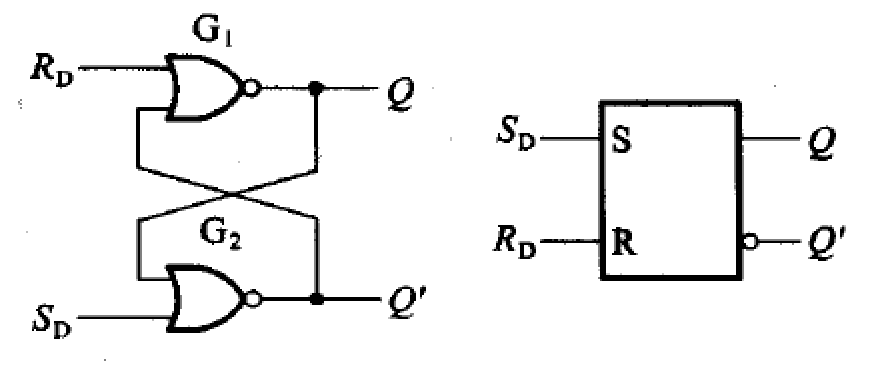

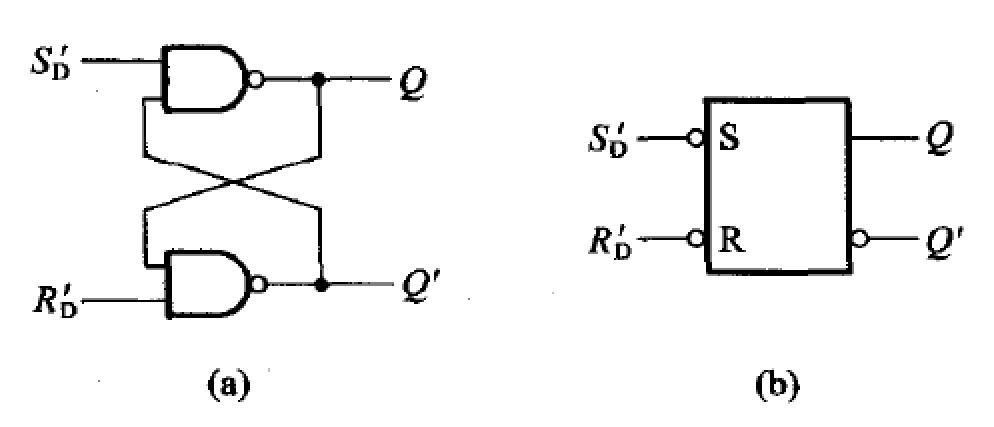

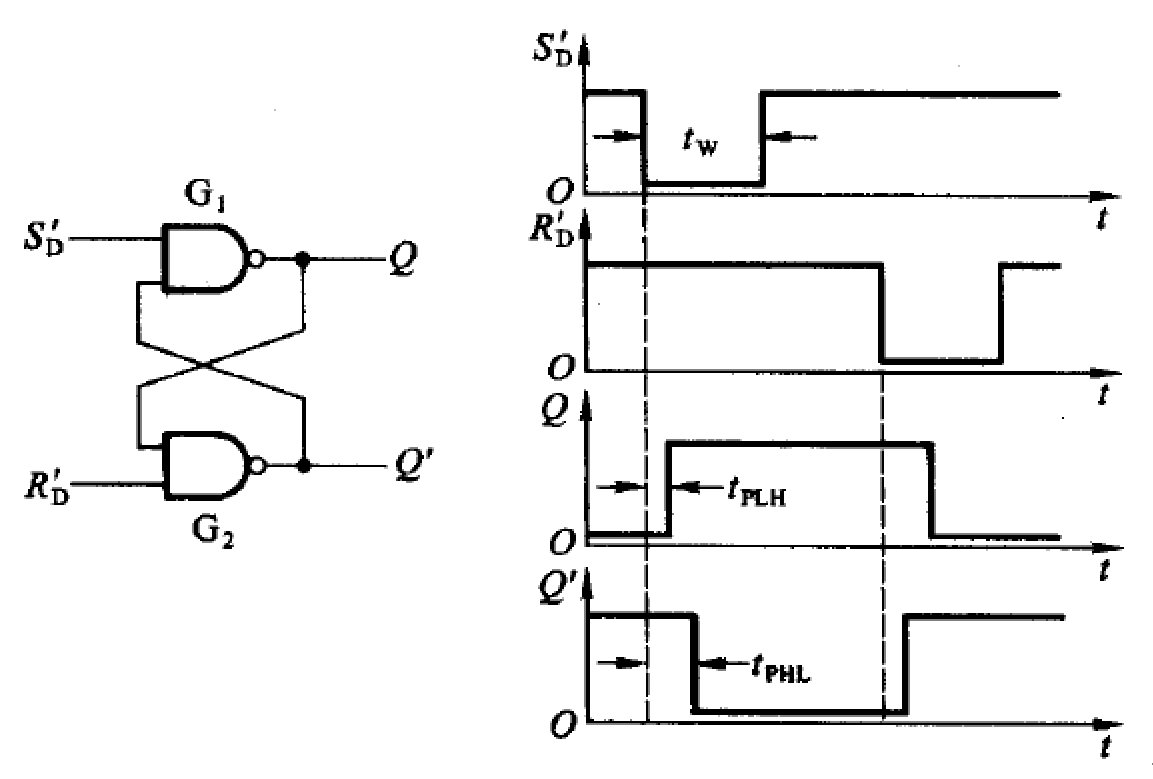

5.1 SR锁存器

是接下来要介绍的各种触发器电路的基本构成部分。

$S_D$为置位端,$R_D$为复位端。

$S_D’$为置位端,$R_D’$为复位端,以低电平作为输入信号,或称低电平有效。

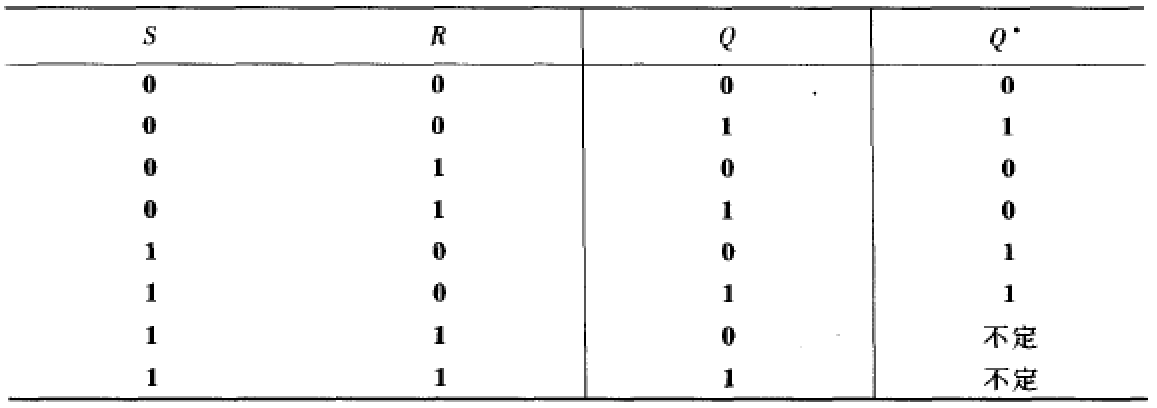

$S_D$和$R_D$的$”1”$信号同时消失后,$Q^\star$不定,所以约束条件:$S_DR_D=0$

5.2 触发器

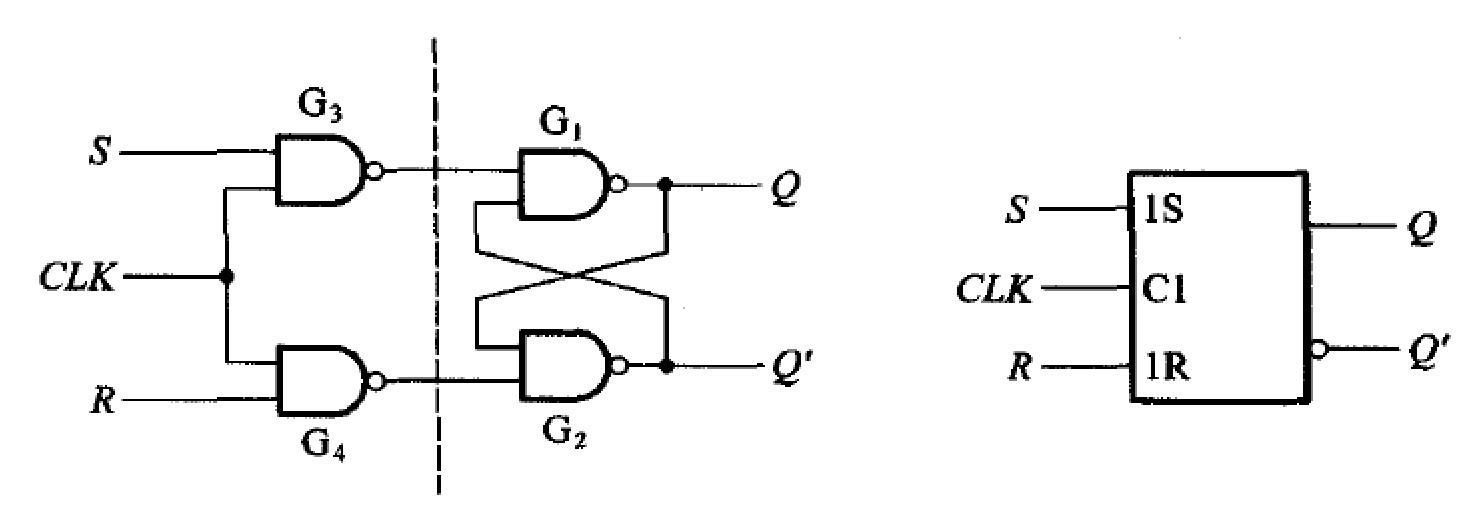

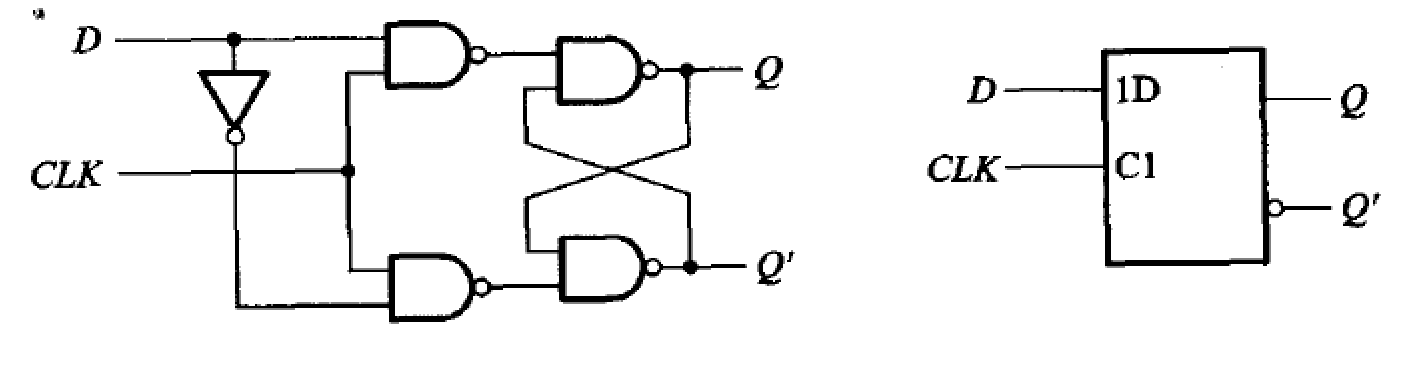

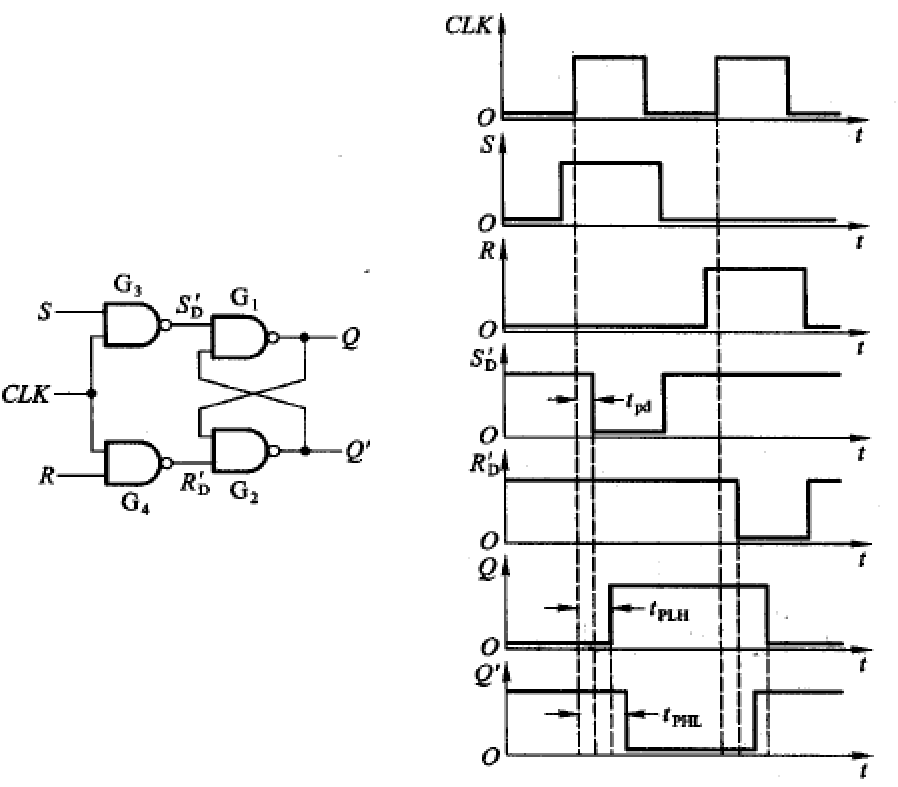

5.2.1 电平触发的触发器

增加了一个触发信号输入端CLK。

当$CLK=0$时,输出保持不变;当$CLK=1$时,触发器可以起作用。

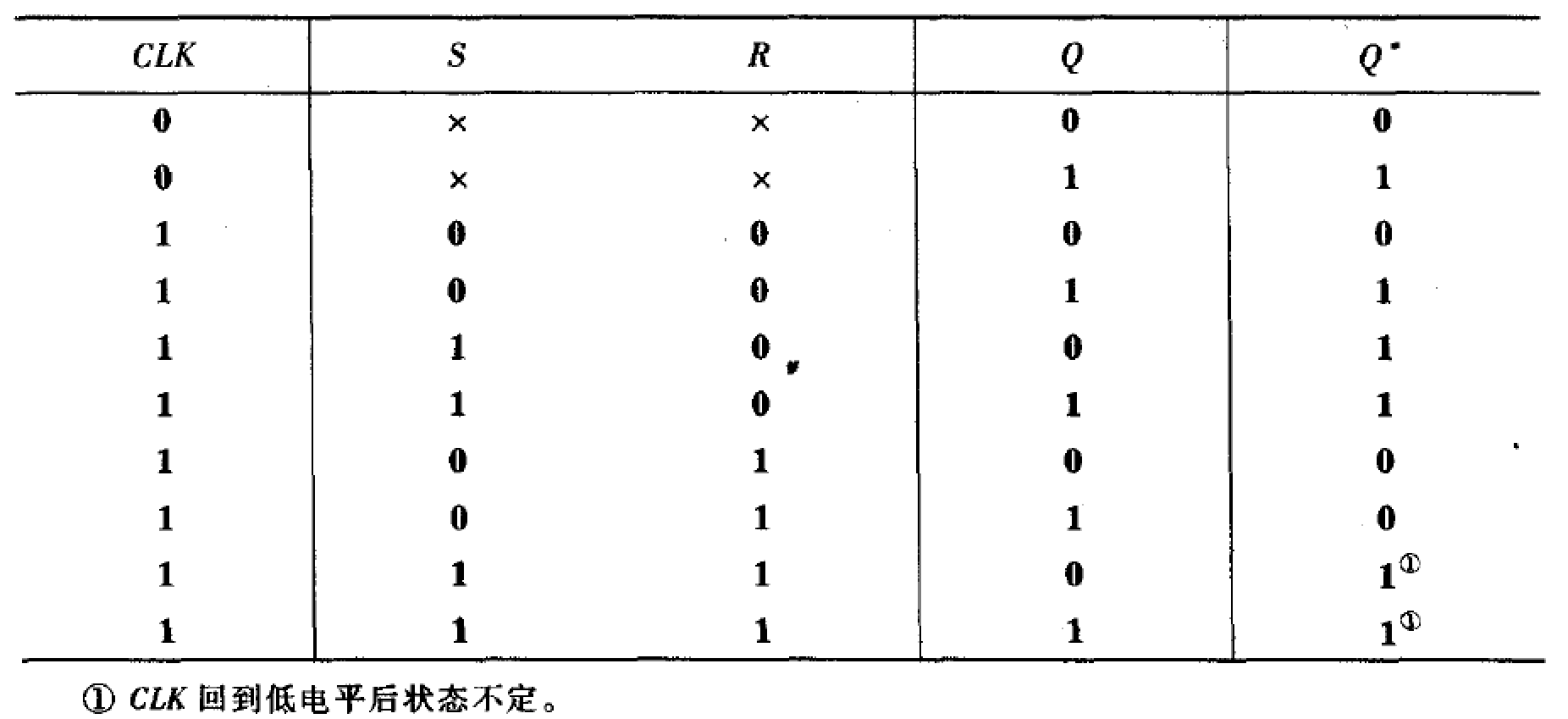

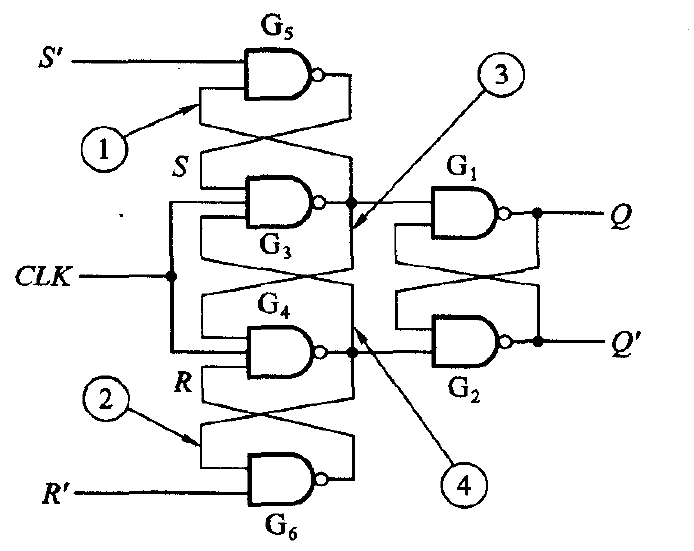

有时需要在$CLK$的有效电平到达之前预先将触发器置成指定的状态,为此设置有异步置$1$输入端$S’_D$和异步置$0$输入端$R’_D$

在$CLK=1$期间,$S、R$的状态多次发生变化,那么触发器输出的状态也将发生多次翻转,这就降低了触发器的抗干扰能力。

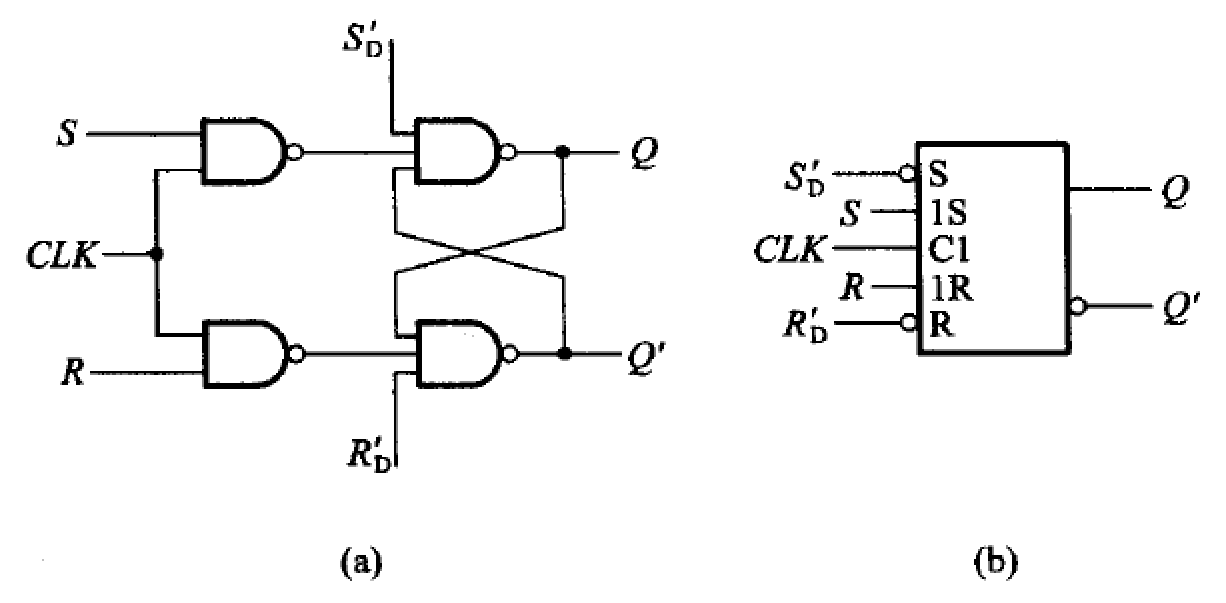

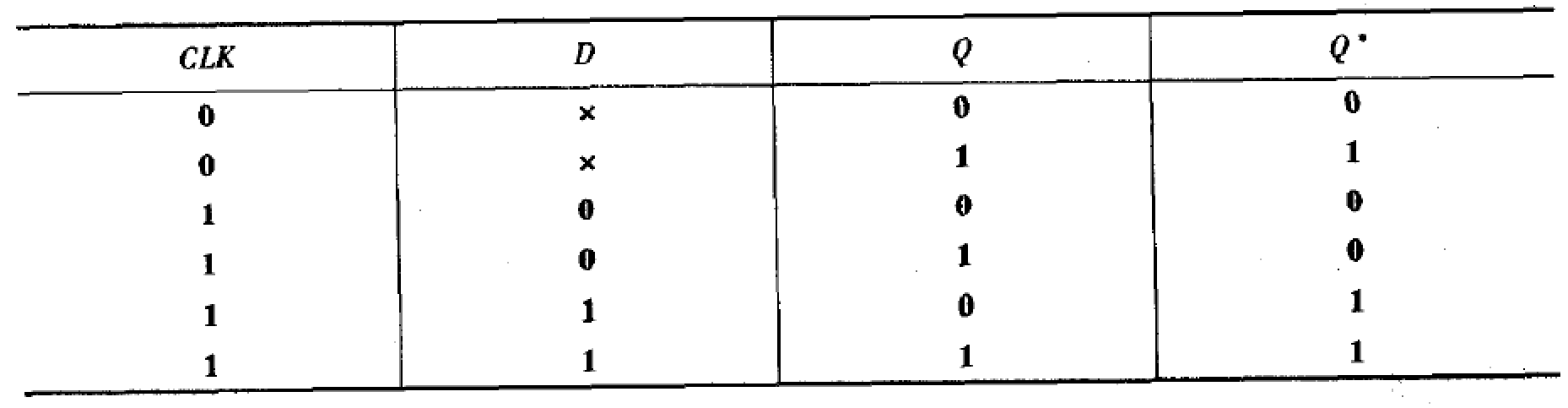

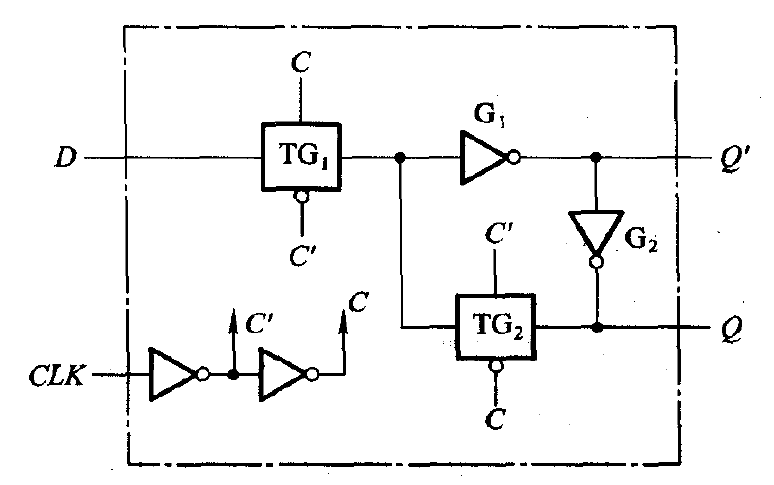

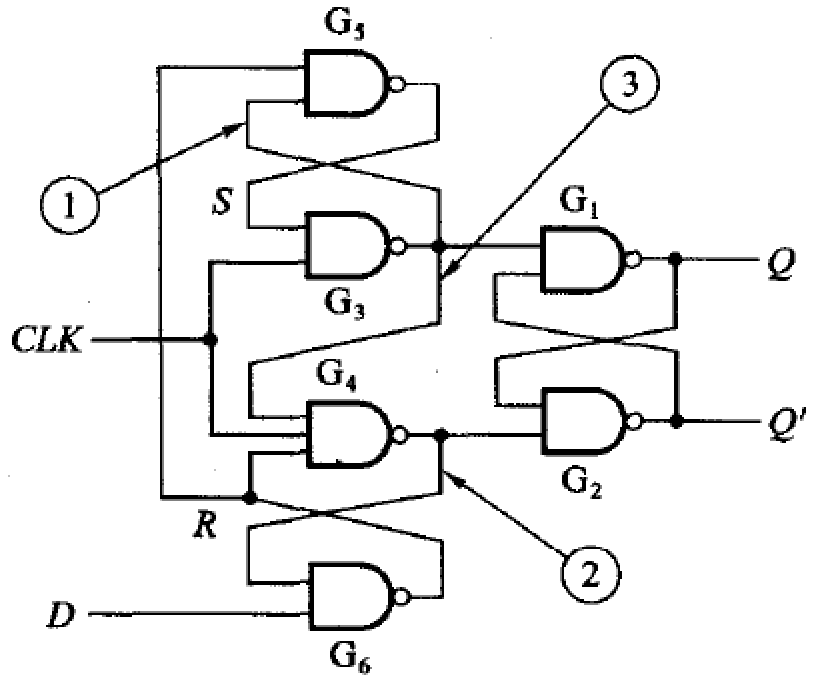

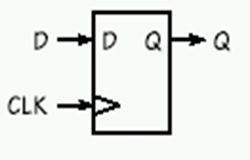

为了能适应单端输入信号的需要,出现了电平触发的D触发器。

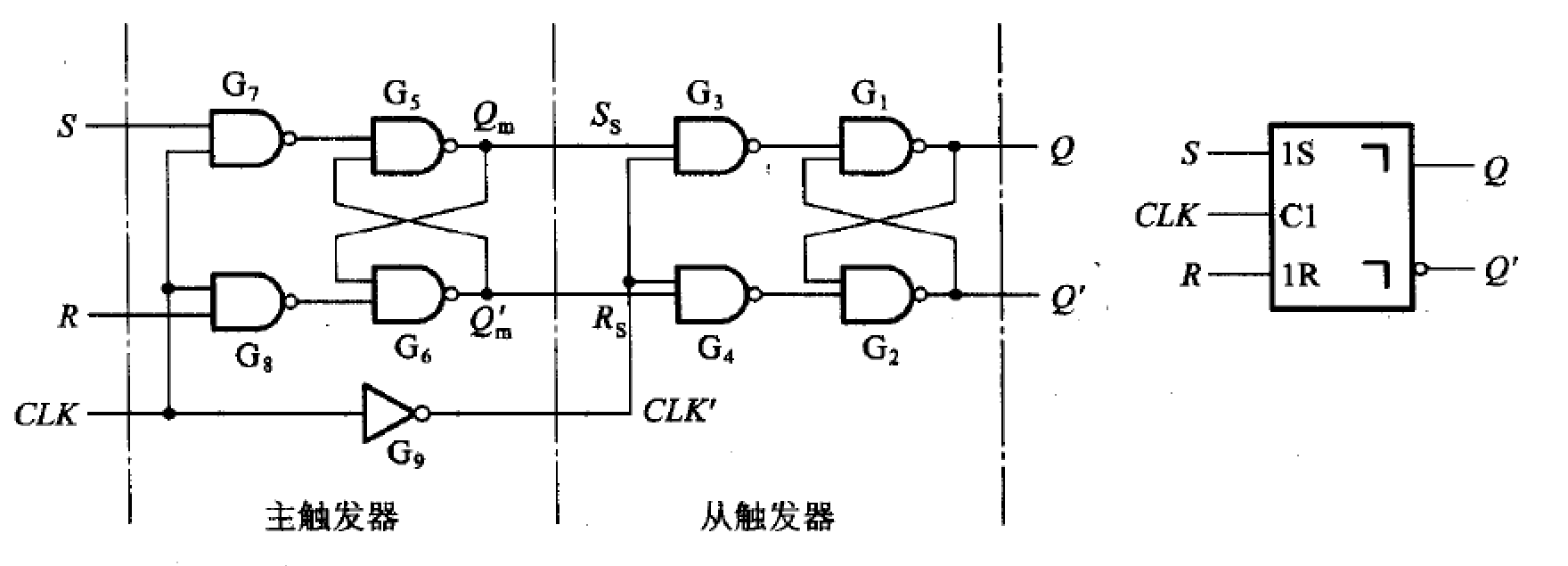

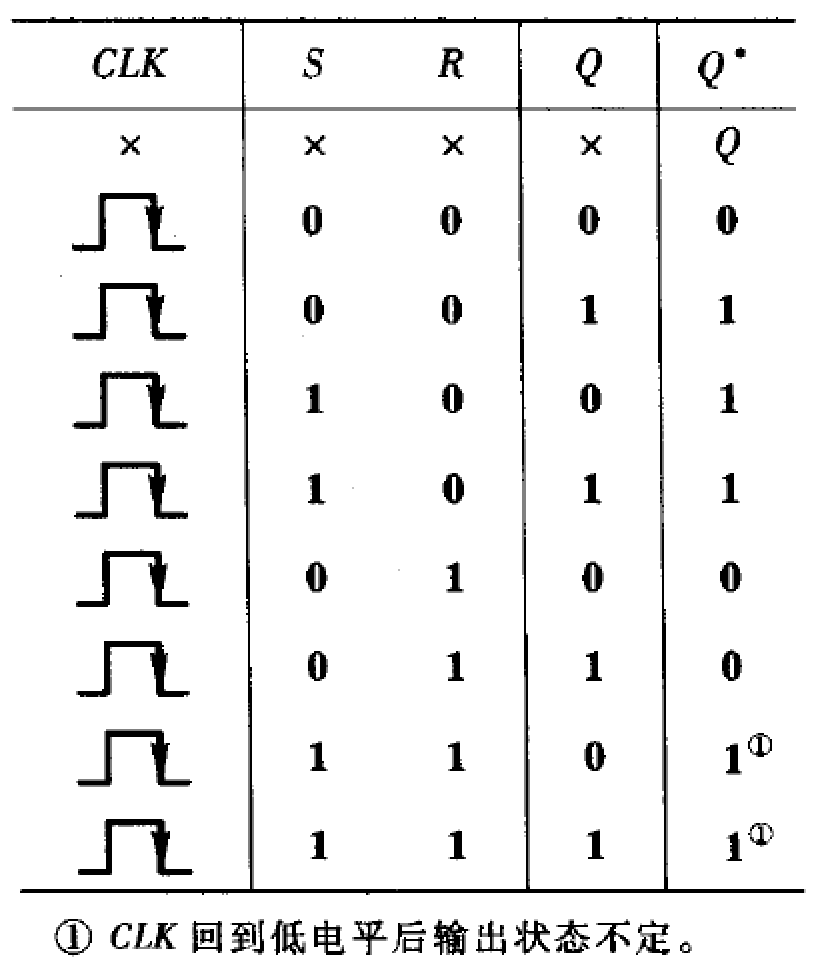

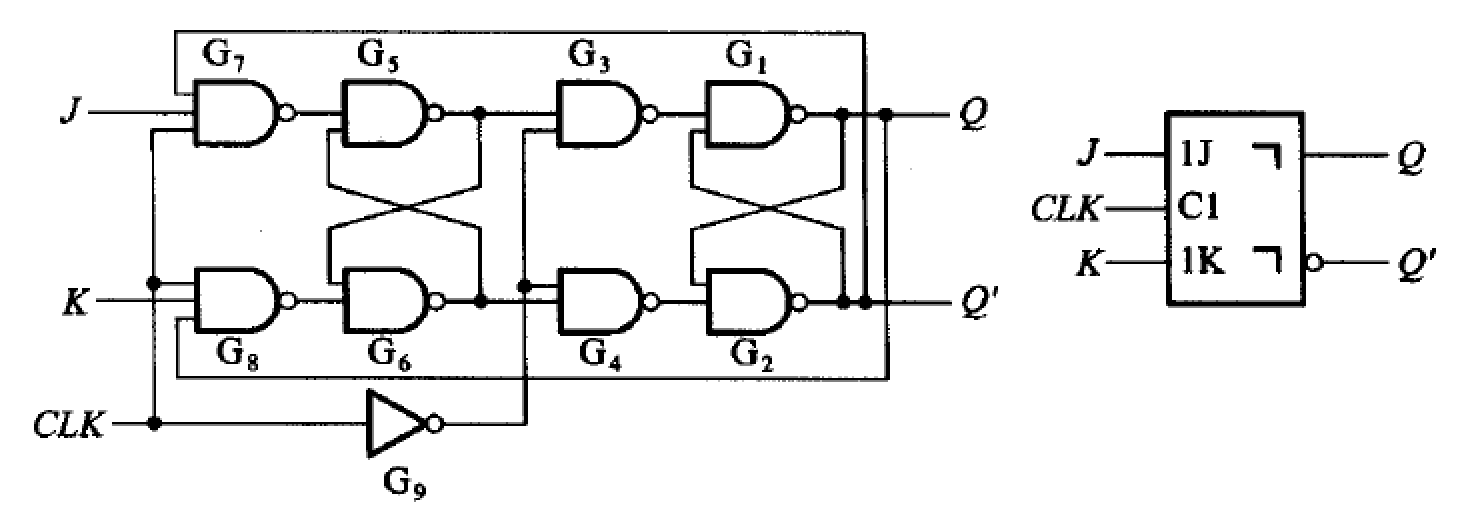

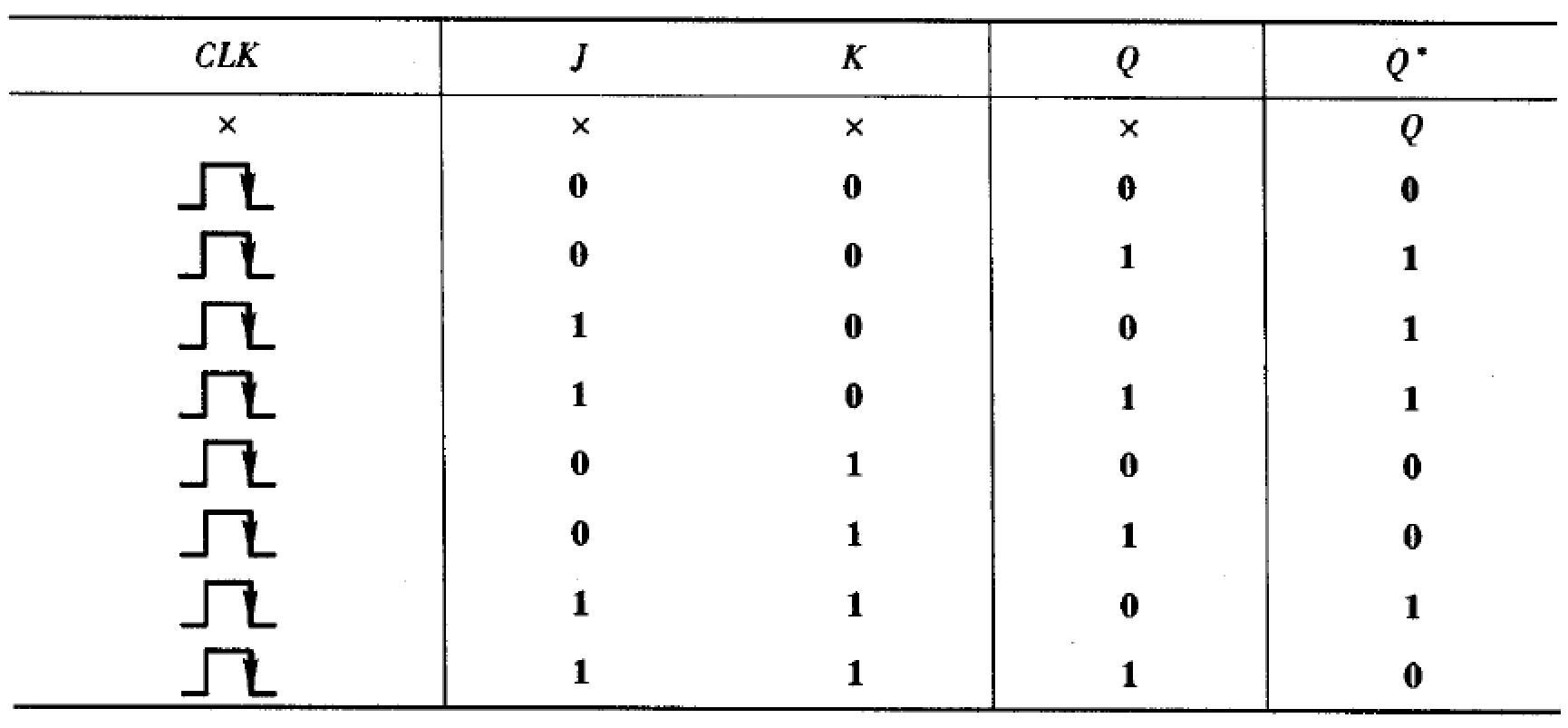

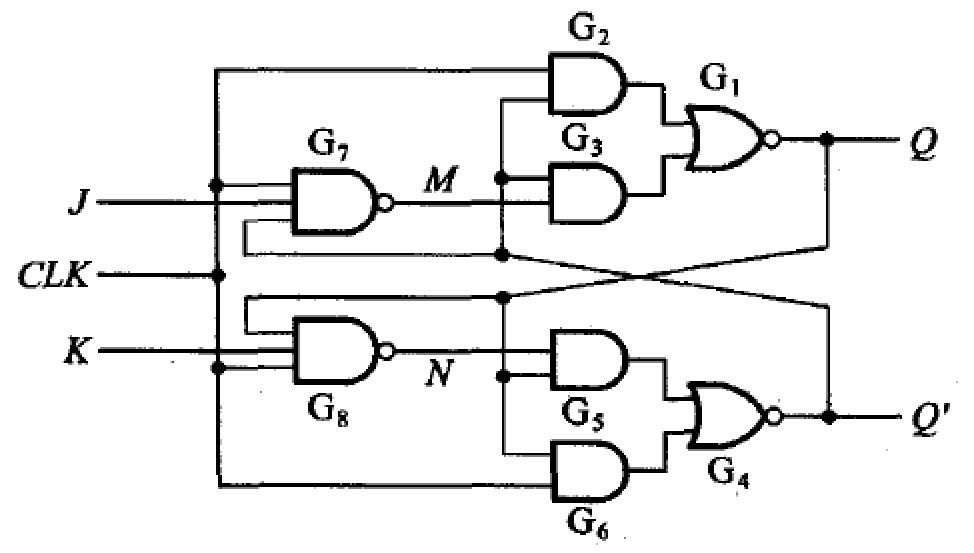

5.2.2 脉冲触发的触发器

在每个$CLK$周期里输出端的状态只能改变一次。

- 当$CLK=1$时,主触发器根据$S$和$R$的状态翻转,从触发器保持原状态不变

- 当$CLK$由高电平返回低电平后,主触发器的状态不再改变,从触发器按照与主触发器相同的状态翻转

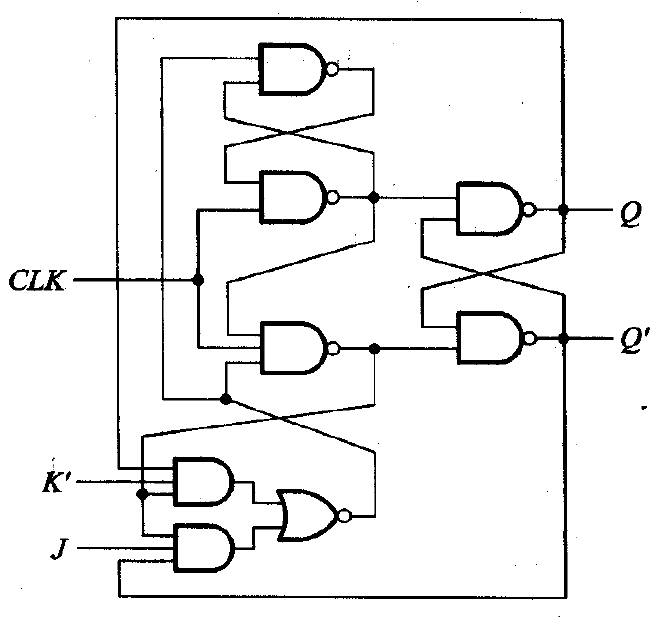

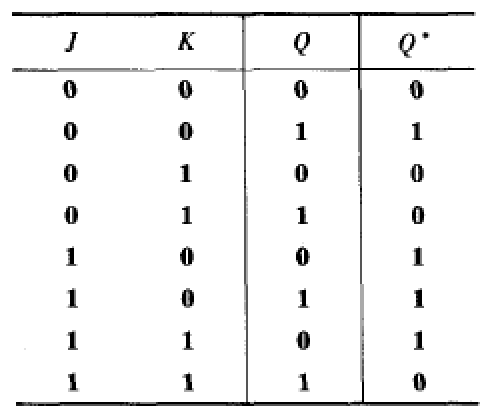

- $J=1,K=0$时,$Q^\star=1$

- $J=0,K=1$时,$Q^\star=0$

- $J=K=0$时,$Q^\star=Q$

- $J=K=1$时,$Q^\star=Q’$

对于主从$JK$触发器,在$CLK=1$期间主触发器只有可能翻转一次。

- $Q=0$时,只允许$J=1$的信号进入主触发器

- $Q=1$时,只允许$K=1$的信号进入主触发器

5.2.3 边沿触发的触发器

动作特点:次态仅仅取决于$CLK$信号下降沿(或上升沿)到达时刻输入信号的状态。

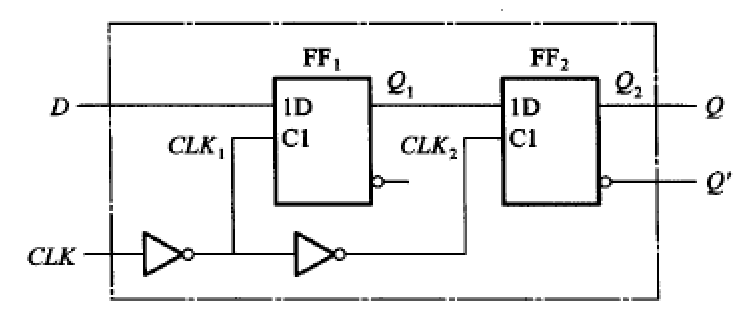

用两个电平触发D触发器组成的边沿触发器

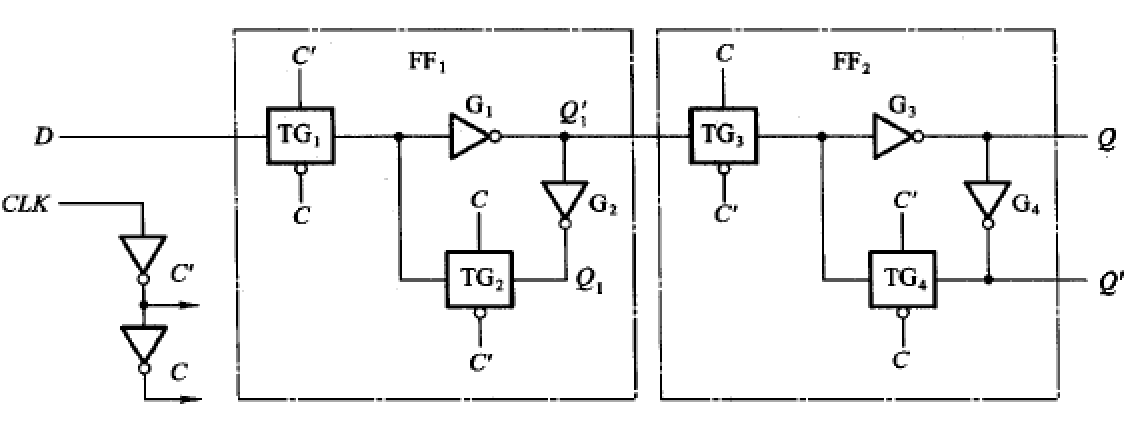

维持阻塞结构边沿触发器

维持阻塞结构SR触发器

维持阻塞结构D触发器

维持阻塞结构JK触发器

利用门电路传输延迟时间的边沿触发器

边沿JK触发器

输出仅和CLK上升沿时刻的输入状态有关。

5.3 触发器的逻辑功能及其描述方法

5.3.1 触发器按逻辑功能的分类

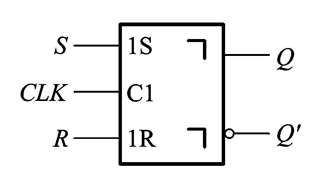

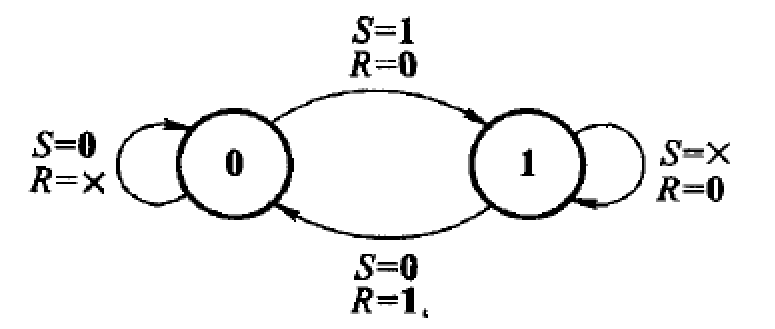

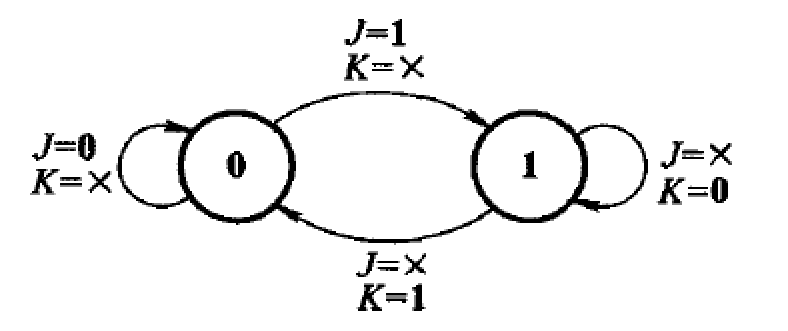

RS触发器

特性方程:

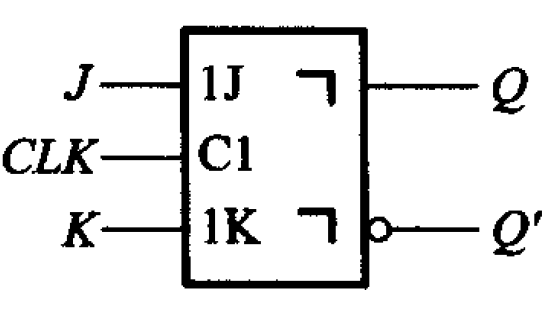

JK触发器

特性方程:

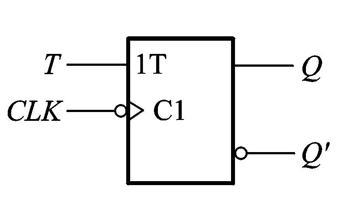

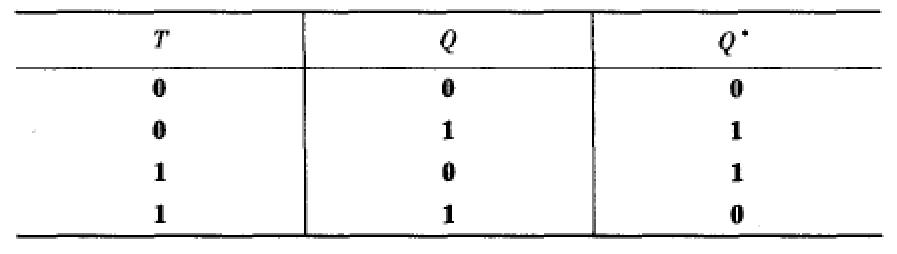

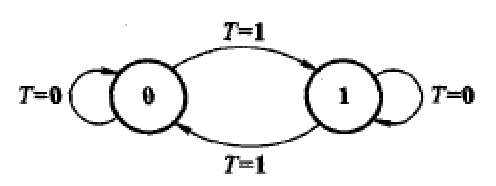

T触发器

特性方程:

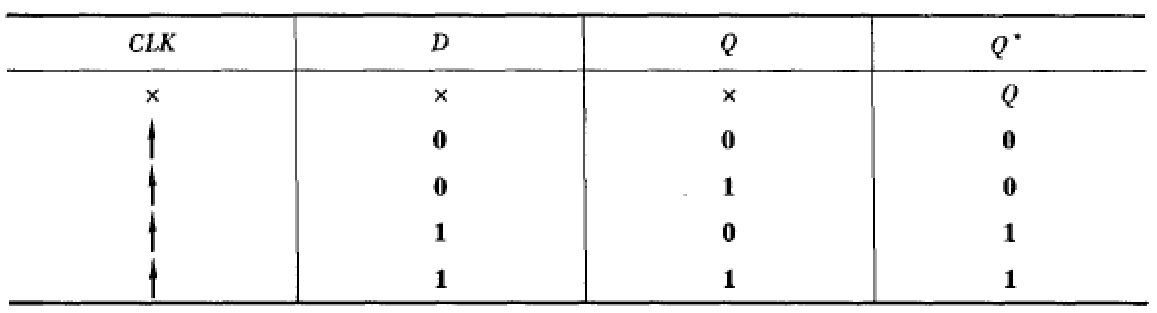

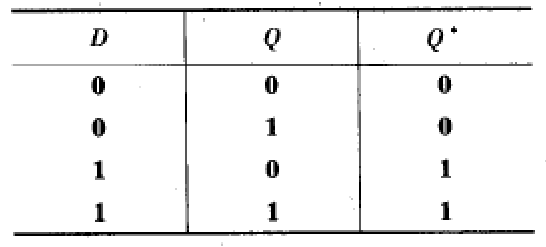

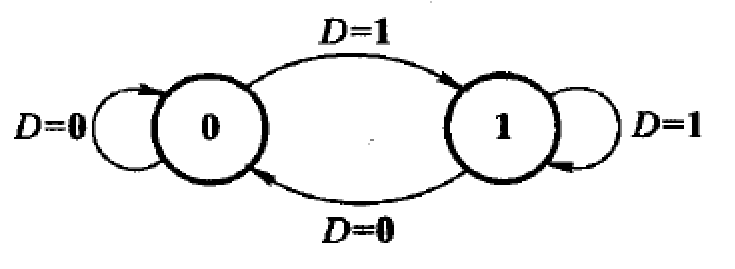

D触发器

特性方程:

触发器的电路结构和逻辑功能、触发方式的关系:

①. 触发器的电路结构和逻辑功能之间不存在固定的对应关系

②. 触发器的电路结构和触发方式之间存在固定的对应关系

5.4 触发器的动态特性

5.4.1 SR锁存器的动态特性

输入信号宽度:$t_w\ge 2t_{pd}$($t_{pd}$为门电路的平均传输延迟时间)

传输延迟时间:从输入信号到达起到锁存器输出端新状态稳定地建立起来为止经过的时间。

- 输出端从低电平变为高电平的传输延迟时间:$t_{PLH}=t_{pd}$

- 输出端从高电平变为低电平的传输延迟时间:$t_{PLL}=2t_{pd}$

5.4.2 电平触发RS触发器的动态特性

输入信号宽度:$S$(或$R$)和$CLK$同时为高电平的时间应满足:$t_{W(S\cdot CLK)}\ge 2t_{pd}$

传输延迟时间:从$S$(或$R$)和$CLK$同时变为高电平开始,到输出端新状态稳定地建立起来为止所经过的时间

- $t_{PLH}=2t_{pd}$

- $t_{PHL}=3t_{pd}$

5.4.3 主从触发器的动态特性

为避免$CLK$下降沿到达时主触发器的状态与$J、K$的状态不符,通常应使$J、K$的状态在$CLK=1$期间保持不变。

建立时间:输入信号应先于$CLK$动作沿到达的时间,$t_{set}=2t_{pd}$

保持时间:$CLK$下降沿到达后输入信号仍需要保持不变的时间;保持时间必须大于$CLK$的下降时间$t_f$,$t_H\ge t_f$

传输延迟时间:从$CLK$下降沿开始到输出端新状态稳定地建立起来的时间

- $t_{PLH}=3t_{pd}$

- $t_{PHL}=4t_{pd}$

最高时钟频率:保证主触发器的可靠翻转

5.4.4 维持阻塞触发器的动态特性

建立时间:(在$CLK$上升沿到达之前输出端状态必须稳定建立),$D$端的输入信号应先于$CLK$的上升沿的时间,$t_{set}\ge 2t_{pd}$

保持时间:在$CLK$上升沿到达之后输出端状态需保持的时间,$t_{HL}\ge t_{pd}$

传输延时时间:从$CLK$上升沿到达时开始计算,

- $t_{PHL}=3t_{pd}$

- $t_{PLH}=2t_{pd}$

最高时钟频率:

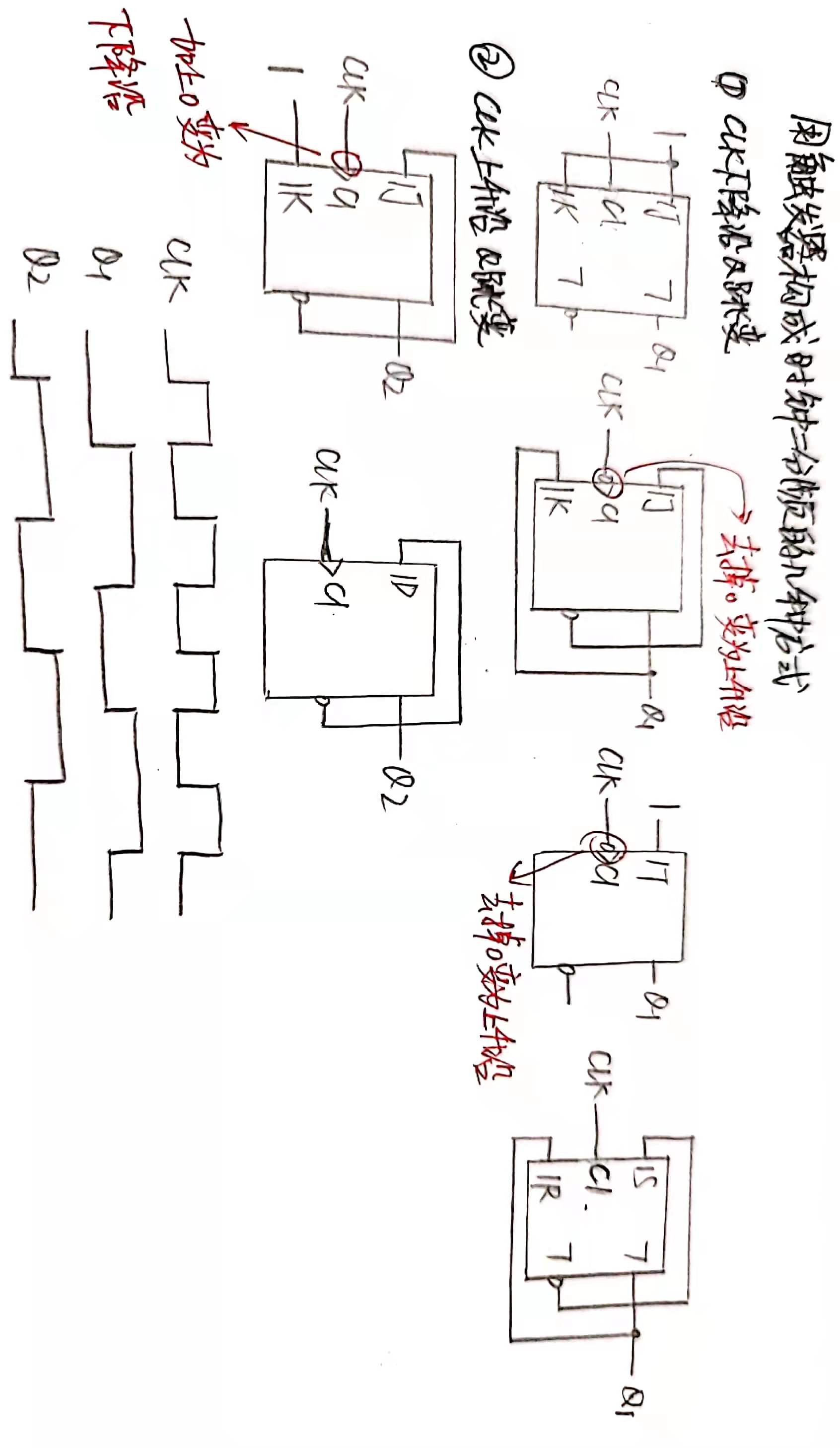

增:用触发器实现二分频

题型总结